SEm/laboratoires/09 pipeline

From FSI

Revision as of 11:34, 28 April 2016 by Francois.corthay (Talk | contribs)

|

Additionneur rapide

Introduction

Dans ce laboratoire, nous allons reprendre un additionneur rapide utilisant la technique du "pipeline".

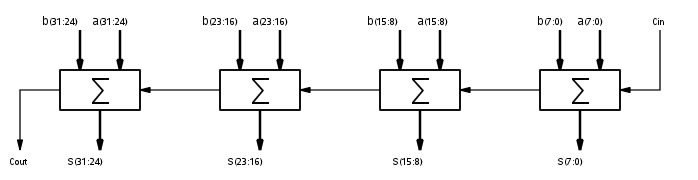

Additionneur combinatoire

L'additionneur rapide se basera sur la mise en série d'additionneurs plus petits.

Additionneur itératif

L'additionneur rapide utilisera un ensemble d'additionneurs combinatoires.

L'architecture noPipe donne un exemple de description VHDL d'un système itératif

par le placement de composants à l'aide d'une boucle for … generate.

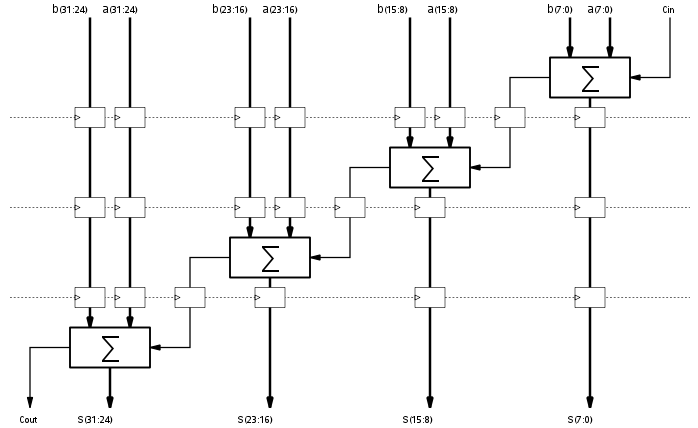

Additionneur rapide

L'additionneur rapide se fait en insérant des bascules entre les additionneurs combinatoires.

Navigation

![]() Main Page

Main Page

![]() Travaux de laboratoire

-

Travaux de laboratoire

- ![]()