Automatische Synthese

Einleitung

Dieses Labor zeigt die automatische Synthese von VHDL-Code.

Es basiert auf dem Beispiel des Funktionsgenerators.

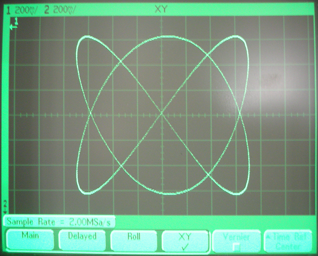

Die Zusammensetzung von zwei verschiedenen Sinuswellen erlaubt es Lissajous-Figuren zu zeichnen.

Synthese

Auf das obersten Level der zu erstellenden Schaltung kommen die Ein- / Ausgangsblöcke.

Hier findet man z.B. Polaritätsadapter, Tri-State-Puffer, Synchronisationslogik, ...

In unserem Beispiel werden wir zwei Sinusgeneratoren, zwei Sigma-Delta-Modulatoren und eine Synchronisationslogik für das Reset-Signal setzten.

Wir werden auch den Viereck-Ausgang eines der Generatoren verwenden um ein Synchronisationssignal für das Oszilloskop zu erstellen.

Die Schaltung befindet sich in der Library Board, die Testbank in der Library SineInterpolator_test.

Schaltung

Öffnen Sie den Block FPGA_sineGen in der Library Board, kompilieren Sie ihn und überprüfen Sie per Simulation ob die Schaltung in Ordnung ist.

Eine Simulation der Schaltung auf diesem Level erlaubt es die Funktionalität des Systems sicherzustellen.

Interpolationskoeffizienten

Die von Ihnen berechneten Koeffizienten können mit der nebenstehenden Waveform überprüft werden.

Erstellung der Datei

Starten Sie den Task Prepare for synthesis.

Synthese

- Starten Sie den Task Xilinx Project Navigator.

- Geben Sie den Schaltugstyp an, xc3s500E, und geben Sie dessen Parameter, FG320-5.

- Fügen Sie Sie die erzeugte VHDL Datei sineGen.vhd zum Projekt hinzu.

- Stellen Sie sicher, dass FPGA_sineGen-struct die ausgewählte Schaltung ist.

- Fügen Sie Sie die Datei sineGen.ucf zum Projekt hinzu.

- Starten Sie den Befehl Synthesize - XST.

- Prüfen Sie alle Warnungen ("warning") und stellen Sie sicher, dass die Schaltung keine Realisierungsprobleme aufweist.

- Überprüfen Sie die Grösse der resultierenden Schaltung.

- Finden Sie die maximale Taktfrequenz, die für diese Schaltung möglich ist.

Place und Route

Starten Sie den Befehl Implement Design.

Konfiguration

- Speisen Sie das FPGA-Board und schliessen Sie das JTAG-Downloadkabel an.

- Starten Sie die Befehle Generate Programming File und Configure Target Device.

- Laden Sie die Konfiguration ins FPGA.

Tests

Schalten Sie die Tiefpassfilter an die Ausgänge der Modulatoren.

Prüfen Sie die Sinuswellen auf dem Oszilloskop.

Stellen Sie den Display auf X-Y Modus ein: Sie sollten nun die Lissajous-Figur sehen.

Navigation

03 Digital / Analog Wandler

03 Digital / Analog Wandler

Anleitung auf Deutsch

05 Zustandsmaschine

Anleitung auf Deutsch

05 Zustandsmaschine

![]() 03 Digital / Analog Wandler

03 Digital / Analog Wandler

![]() Anleitung auf Deutsch

05 Zustandsmaschine

Anleitung auf Deutsch

05 Zustandsmaschine ![]()