SEm/labore/09 high speed addierer

(→High-speed Zähler) |

|||

| (6 intermediate revisions by one user not shown) | |||

| Line 8: | Line 8: | ||

== Kombinatorischer Addierer == | == Kombinatorischer Addierer == | ||

| − | Der High-speed Addierer wird durch kleine, in | + | Der High-speed Addierer wird durch kleine, in Serie geschaltenen Addierern realisiert. |

{{TaskBox|content= | {{TaskBox|content= | ||

| Line 16: | Line 16: | ||

== Iterativer Addierer == | == Iterativer Addierer == | ||

| − | Der High-speed Addierer verwendet eine Zusammensetzung | + | Der High-speed Addierer verwendet eine Zusammensetzung aus kombinatorischen Addierern. In einem ersten Schritt wird dieser Addierer noch ohne Pipeline implementiert, um zu verstehen, wie Komponenteninstanzen und Schleifen in VHDL benutzt werden können. |

[[File:Sem labs iterative adder.svg|center|Iterativer Addierer]] | [[File:Sem labs iterative adder.svg|center|Iterativer Addierer]] | ||

| Line 24: | Line 24: | ||

}} | }} | ||

| − | Die Architektur <code>noPipe</code>, zeigt ein Beispiel, wie eine iterative Struktur anhand einer | + | Die Architektur <code>noPipe</code>, zeigt ein Beispiel, wie eine iterative Struktur anhand einer <code>for … generate</code> Schleife implementiert werden kann. |

| − | <code>for … generate</code>. | + | |

{{TaskBox|content= | {{TaskBox|content= | ||

| Line 39: | Line 38: | ||

{{TaskBox|content= | {{TaskBox|content= | ||

| − | In der Library <code>pipelinedOperators</code> ist die Architektur <code>studentVersion</code> sowie die Default-Architektur <code>pipelineAdder</code> gegeben. | + | In der Library <code>pipelinedOperators</code> ist die Architektur <code>studentVersion</code>, sowie die Default-Architektur <code>pipelineAdder</code> gegeben. |

}} | }} | ||

| Line 48: | Line 47: | ||

== High-speed Zähler == | == High-speed Zähler == | ||

| − | Der High-speed Zähler kann eine neue Summe zu jeder Taktperiode liefern. | + | Der High-speed Zähler kann eine neue Summe zu jeder Taktperiode liefern. Jedoch wird es eine gewisse Anzahl Taktperioden dauern, bis die neue Summe zur Verfügung steht. |

{{TaskBox|content= | {{TaskBox|content= | ||

| − | + | Schreiben Sie die Architektur des Zählers in VHDL <code>pipelineCounter</code> und stellen Sie sicher, dass dieser ordnungsgemäss aufzählt. | |

}} | }} | ||

Latest revision as of 16:00, 14 May 2018

|

High-speed Addierer

Einleitung

In diesem Labor werden wir einen High-speed Addierer mithilfe der Pipeline-Technologie implementieren.

Kombinatorischer Addierer

Der High-speed Addierer wird durch kleine, in Serie geschaltenen Addierern realisiert.

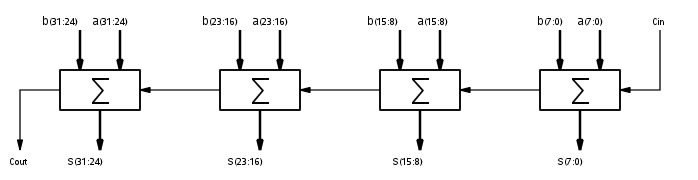

Iterativer Addierer

Der High-speed Addierer verwendet eine Zusammensetzung aus kombinatorischen Addierern. In einem ersten Schritt wird dieser Addierer noch ohne Pipeline implementiert, um zu verstehen, wie Komponenteninstanzen und Schleifen in VHDL benutzt werden können.

Die Architektur noPipe, zeigt ein Beispiel, wie eine iterative Struktur anhand einer for … generate Schleife implementiert werden kann.

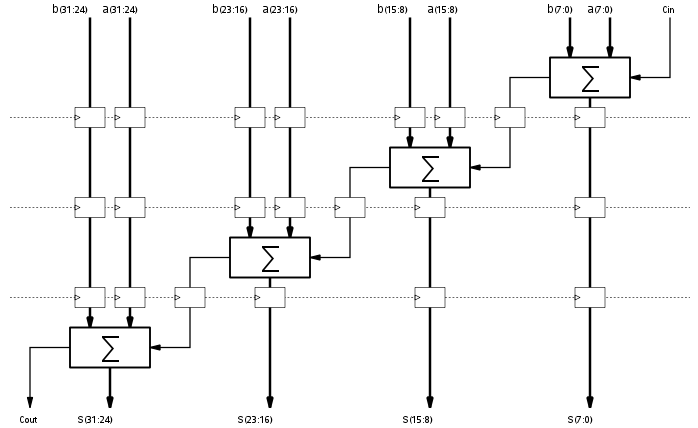

High-speed Addierer

Für den High-speed Addierer werden FlipFlops zwischen den kombinatorischen Adddierern hinzugefügt.

High-speed Zähler

Der High-speed Zähler kann eine neue Summe zu jeder Taktperiode liefern. Jedoch wird es eine gewisse Anzahl Taktperioden dauern, bis die neue Summe zur Verfügung steht.

Navigation

![]() 08 Realisierung eines AMBA-SoCs

08 Realisierung eines AMBA-SoCs

![]() Laborprojekte

-

Laborprojekte

- ![]()