Hardware/FPGAEBS/Configuration

From UIT

|

General

After designing and simulating your design based on VHDL Template Design, you have to prepare it:

- In HDL-Designer: Perform Task Flow Prepare for Synthesis

- Generates all VHDL Files

- Concatenates them into a single VHDL File

- Trims work libraries

- In HDL-Designer: Perform Task Flow Xilinx Project Navigator

- Updates the ISE (*.xise) Project file

- Launches ISE

- In ISE: Perform Task Generate Programming File

- Runs Synthesis

- Runs P&R

- Generate Programming File *.bit

- In ISE: Perform Task Configure Target Device

- Launches Impact

After that you can either way download the file directly to the FPGA or create another file to download to the non-volatile memory.

FPGA Configuration

Flash Writing

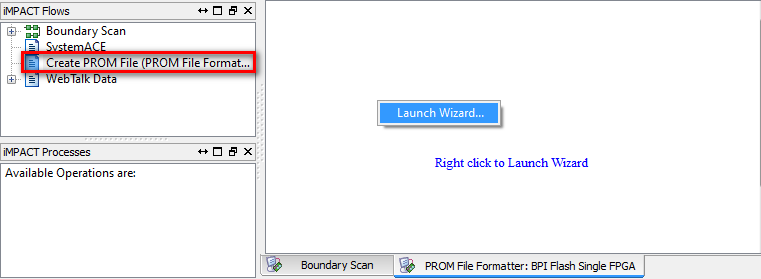

To program the xcf04s Platform Flash In-System Programmable Configuration PROM you need to turn your *.bit into an *.mcs file. This file can then be used to program the Platform Flash through JTAG.

Flash programming works ONLY with Official Xilinx USB Programmer