Hardware/Parallelport/heb synchro

From UIT

(Difference between revisions)

(→Synchro) |

|||

| (One intermediate revision by one user not shown) | |||

| Line 1: | Line 1: | ||

{{TOC right}} | {{TOC right}} | ||

| − | == Synchro == | + | == Synchro board and assembly == |

The board was designed for the [http://wiki.hevs.ch/ete/index.php5/Main_Page ETE] [http://wiki.hevs.ch/ete/index.php5/Synchro ELN-synchro lab]. | The board was designed for the [http://wiki.hevs.ch/ete/index.php5/Main_Page ETE] [http://wiki.hevs.ch/ete/index.php5/Synchro ELN-synchro lab]. | ||

| Line 11: | Line 11: | ||

|- | |- | ||

! Version || Photo || Schematics || Stock | ! Version || Photo || Schematics || Stock | ||

| + | |- | ||

| + | | V2.0 ||[[File:HEB Synchro v2.jpg|200px|HEB-Synchro]] || [[Media:FPGA_PP_HEB_synchro.pdf|HEB-Synchro Schematic PDF]] || [[Hardware/Stock_PP#HEB_Synchro|16fully mounted]] | ||

|- | |- | ||

| V1.0 ||[[File:HEB Synchro v1.jpg|200px|HEB-Synchro]] || [[Media:FPGA_PP_HEB_synchro.pdf|HEB-Synchro Schematic PDF]] || [[Hardware/Stock_PP#HEB_Synchro|12 fully mounted]] | | V1.0 ||[[File:HEB Synchro v1.jpg|200px|HEB-Synchro]] || [[Media:FPGA_PP_HEB_synchro.pdf|HEB-Synchro Schematic PDF]] || [[Hardware/Stock_PP#HEB_Synchro|12 fully mounted]] | ||

Latest revision as of 12:19, 14 October 2021

|

Synchro board and assembly

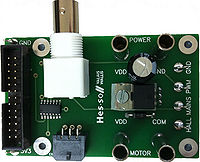

The board was designed for the ETE ELN-synchro lab.

It receives 2 sinewaves: one from a 50 Hz function generator and one from the AC generator. These signals are triggered at 0 V in order to deliver logic-level signals to the FPGA.

The FPGA delivers a PWM output which controls a power switch. The switch then drives the DC motor.

| Version | Photo | Schematics | Stock |

|---|---|---|---|

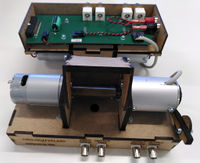

| V2.0 |  |

HEB-Synchro Schematic PDF | 16fully mounted |

| V1.0 |  |

HEB-Synchro Schematic PDF | 12 fully mounted |