SEm/laboratoires/09 pipeline

Axel.amand (Talk | contribs) (→Compteur rapide) |

(→Compteur rapide) |

||

| Line 60: | Line 60: | ||

Ecrire l'architecture VHDL du compteur <code>pipelineCounter</code> et vérifier son bon fonctionnement. | Ecrire l'architecture VHDL du compteur <code>pipelineCounter</code> et vérifier son bon fonctionnement. | ||

}} | }} | ||

| + | |||

| + | == Comparaison == | ||

| + | |||

| + | Le compteur avec pipeline devrait en principe pouvoir fonctionner à plus haute vitesse | ||

| + | qu'un compteur avec un additionneur combinatoire, à propagation de report. | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Effectuer la synthèse du compteur avec les deux variantes de l'additionneur et comparer les vitesses de fonctionnement. | ||

| + | }} | ||

| + | |||

| + | Avec la sélection de l'additionneur combinatoire (architecture <code>noPipe</code>), | ||

| + | le fonctionnement ne serait pas correct, | ||

| + | mais le but ici est uniquement de comparer les vitesses de fonctionnement. | ||

{{navNamed | {{navNamed | ||

Latest revision as of 09:00, 2 May 2022

|

Additionneur rapide

Introduction

Dans ce laboratoire, nous allons reprendre un additionneur rapide utilisant la technique du "pipeline".

Additionneur combinatoire

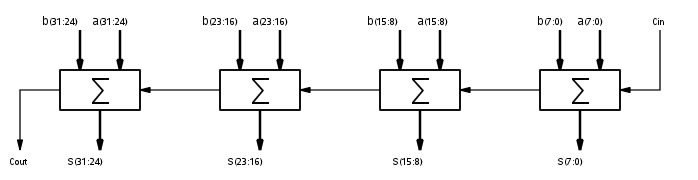

L'additionneur rapide se basera sur la mise en série d'additionneurs plus petits.

Additionneur itératif

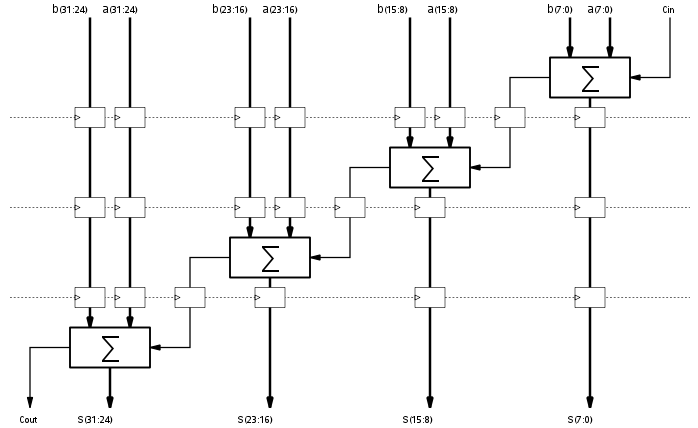

L'additionneur rapide utilisera un ensemble d'additionneurs combinatoires. Cet additionneur est réalisé dans un premier temps dans le but de comprendre la manière de décrire un circuit en VHDL en instanciant des composants à l'aide de boucles.

L'architecture noPipe, mise à disposition, donne un exemple de description VHDL d'un système itératif

par le placement de composants à l'aide d'une boucle for … generate.

Additionneur rapide

L'additionneur rapide se fait en insérant des bascules entre les additionneurs combinatoires.

Compteur rapide

L'additioneur rapide est capable de fournir une nouvelle somme à chaque période d'horloge. Il lui faut cependant un certain nombre de périodes d'horloge avant de fournir le résultat de la somme.

Comparaison

Le compteur avec pipeline devrait en principe pouvoir fonctionner à plus haute vitesse qu'un compteur avec un additionneur combinatoire, à propagation de report.

Avec la sélection de l'additionneur combinatoire (architecture noPipe),

le fonctionnement ne serait pas correct,

mais le but ici est uniquement de comparer les vitesses de fonctionnement.

Navigation

![]() 08 Réalisation d'un SoC AMBA

08 Réalisation d'un SoC AMBA

![]() Travaux de laboratoire

-

Travaux de laboratoire

- ![]()