Components/IP/NanoBlaze

(Difference between revisions)

(→Assembler) |

|||

| Line 21: | Line 21: | ||

With this, the assembler can easily be integrated in the [[Tools/Mentor_HDL_Designer|Mentor HDL Designer]] environment. | With this, the assembler can easily be integrated in the [[Tools/Mentor_HDL_Designer|Mentor HDL Designer]] environment. | ||

| − | The processor includes a disassembler which writes the current instruction in the form of a string. | + | The VHDL processor code includes a disassembler process which writes the current instruction in the form of a string. |

| − | This can be displayed in the simulator. | + | This string can be displayed in the simulator for debugging purpose. |

| − | The corresponding VHDL code is commented out for synthesis via the <code> | + | The corresponding VHDL code is commented out for synthesis via the <code>pragma translate_off</code> clause. |

= Sources = | = Sources = | ||

This IP is found in the HEVs EDA Repository: svn: https://repos.hevs.ch/svn/eda/ | This IP is found in the HEVs EDA Repository: svn: https://repos.hevs.ch/svn/eda/ | ||

Revision as of 10:47, 8 April 2015

|

Component

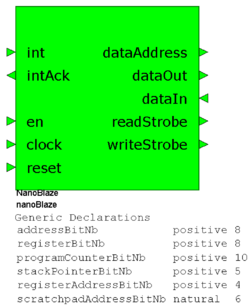

The NanoBlaze is a grow-up of the Xilinx Picoblaze micro controller, hence the name. Various sizes can be defined with the help of generic parameters:

registerBitNbdefines the data bit widthprogramCounterBitNballows to cope with different program lengthsstackPointerBitNbadapts to various nesting depths of the subroutinesregisterBitNbdefines the data bit widthregisterAddressBitNballows to choose the number of internal registersscratchPadAddressBitNballows to manage the size of the scratchpadaddressBitNbdefines the size of the I/O space

With scratchPadAddressBitNb = 0, the scratchpad is not implemented.

Assembler

It has an assembler written in PERL which runs on any operating system. With this, the assembler can easily be integrated in the Mentor HDL Designer environment.

The VHDL processor code includes a disassembler process which writes the current instruction in the form of a string.

This string can be displayed in the simulator for debugging purpose.

The corresponding VHDL code is commented out for synthesis via the pragma translate_off clause.

Sources

This IP is found in the HEVs EDA Repository: svn: https://repos.hevs.ch/svn/eda/