Components/IP/NanoBlaze

(→Instruction set) |

(→Instruction set) |

||

| Line 34: | Line 34: | ||

= Instruction set = | = Instruction set = | ||

| − | The following table shows the instruction set for an 8 bit processor with 10 address bits: | + | The following table shows the instruction set for an 8 bit processor with 16 registers and 10 program address bits: |

{| class="wikitable" style="text-align:center" | {| class="wikitable" style="text-align:center" | ||

|- | |- | ||

! instruction !! 17 !! 16 !! 15 !! 14 !! 13 !! 12 !! 11 !! 10 !! 9 !! 8 !! 7 !! 6 !! 5 !! 4 !! 3 !! 2 !! 1 !! 0 !! function | ! instruction !! 17 !! 16 !! 15 !! 14 !! 13 !! 12 !! 11 !! 10 !! 9 !! 8 !! 7 !! 6 !! 5 !! 4 !! 3 !! 2 !! 1 !! 0 !! function | ||

| + | |- | ||

| + | ! style="text-align:left" | LOAD sX, kk | ||

| + | | colspan="6" | 000000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | loads constant kk into register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | LOAD sX, (sY) | ||

| + | | colspan="6" | 000001 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | loads register sY into register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | INPUT sX, kk | ||

| + | | colspan="6" | 000100 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | loads I/O value at address kk to register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | INPUT sX, (sY) | ||

| + | | colspan="6" | 000101 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | loads I/O value at address sY to register sX | ||

|- | |- | ||

! style="text-align:left" | FETCH sX, kk | ! style="text-align:left" | FETCH sX, kk | ||

| Line 45: | Line 69: | ||

| style="text-align:left" | loads scratchpad value at address kk to register sX | | style="text-align:left" | loads scratchpad value at address kk to register sX | ||

|- | |- | ||

| − | ! style="text-align:left" | FETCH sX, (sY) | + | ! style="text-align:left; border-bottom: 2px solid grey" | FETCH sX, (sY) |

| colspan="6" | 000111 | | colspan="6" | 000111 | ||

| colspan="4" | sX address | | colspan="4" | sX address | ||

| Line 62: | Line 86: | ||

| colspan="8" | sY address | | colspan="8" | sY address | ||

| style="text-align:left" | applies bitwise AND of register sY pattern to register sX | | style="text-align:left" | applies bitwise AND of register sY pattern to register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | OR sX, kk | ||

| + | | colspan="6" | 001100 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | applies bitwise OR of constant kk pattern to register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | OR sX, sY | ||

| + | | colspan="6" | 001101 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | applies bitwise OR of register sY pattern to register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | XOR sX, kk | ||

| + | | colspan="6" | 001110 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | applies bitwise XOR of constant kk pattern to register sX | ||

| + | |- | ||

| + | ! style="text-align:left; border-bottom: 2px solid grey" | XOR sX, sY | ||

| + | | colspan="6" | 001111 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | applies bitwise XOR of register sY pattern to register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | TEST sX, kk | ||

| + | | colspan="6" | 010010 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | applies bitwise AND between constant kk and register sX, only updates C and Z flags | ||

| + | |- | ||

| + | ! style="text-align:left" | TEST sX, sY | ||

| + | | colspan="6" | 010011 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | applies bitwise AND between register sY and register sX, only updates C and Z flags | ||

|- | |- | ||

! style="text-align:left" | COMPARE sX, kk | ! style="text-align:left" | COMPARE sX, kk | ||

| Line 67: | Line 127: | ||

| colspan="4" | sX address | | colspan="4" | sX address | ||

| colspan="8" | kk value | | colspan="8" | kk value | ||

| − | | style="text-align:left" | | + | | style="text-align:left" | subtracts constant kk from register sX, only updates C and Z flags |

|- | |- | ||

| − | ! style="text-align:left" | COMPARE sX, sY | + | ! style="text-align:left; border-bottom: 2px solid grey" | COMPARE sX, sY |

| colspan="6" | 010101 | | colspan="6" | 010101 | ||

| colspan="4" | sX address | | colspan="4" | sX address | ||

| colspan="8" | sY address | | colspan="8" | sY address | ||

| − | | style="text-align:left" | | + | | style="text-align:left" | subtracts register sY from register sX, only updates C and Z flags |

|- | |- | ||

! style="text-align:left" | ADD sX, kk | ! style="text-align:left" | ADD sX, kk | ||

| Line 98: | Line 158: | ||

| colspan="8" | sY address | | colspan="8" | sY address | ||

| style="text-align:left" | adds register sY and carry bit to register sX | | style="text-align:left" | adds register sY and carry bit to register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | SUB sX, kk | ||

| + | | colspan="6" | 011100 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | subtracts constant kk from register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | SUB sX, sY | ||

| + | | colspan="6" | 011101 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | subtracts register sY from register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | SUBCY sX, kk | ||

| + | | colspan="6" | 011110 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | subtracts constant kk and carry bit from register sX | ||

| + | |- | ||

| + | ! style="text-align:left; border-bottom: 2px solid grey" | SUBCY sX, sY | ||

| + | | colspan="6" | 011111 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | subtracts register sY and carry bit from register sX | ||

| + | |- | ||

| + | ! style="text-align:left" | SLA sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 0000 | ||

| + | | style="text-align:left" | shifts register sX to the left, C flag goes to LSB | ||

| + | |- | ||

| + | ! style="text-align:left" | RL sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 0010 | ||

| + | | style="text-align:left" | rotates register sX to the left, LSB goes to LSB | ||

| + | |- | ||

| + | ! style="text-align:left" | SLX sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 0100 | ||

| + | | style="text-align:left" | shifts register sX to the left, LSB remains in LSB | ||

| + | |- | ||

| + | ! style="text-align:left" | SL0 sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 0110 | ||

| + | | style="text-align:left" | shifts register sX to the left, LSB set to 0 | ||

| + | |- | ||

| + | ! style="text-align:left" | SL1 sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 0111 | ||

| + | | style="text-align:left" | shifts register sX to the left, LSB set to 1 | ||

| + | |- | ||

| + | ! style="text-align:left" | SRA sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 1000 | ||

| + | | style="text-align:left" | shifts register sX to the right, C flag goes to MSB | ||

| + | |- | ||

| + | ! style="text-align:left" | SRX sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 1010 | ||

| + | | style="text-align:left" | shift register sX to the right, MSB remains in MSB | ||

| + | |- | ||

| + | ! style="text-align:left" | RR sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 1100 | ||

| + | | style="text-align:left" | rotates register sX to the right, LSB goes to MSB | ||

| + | |- | ||

| + | ! style="text-align:left" | SR0 sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 1110 | ||

| + | | style="text-align:left" | shifts register sX to the right, LSB set to 0 | ||

| + | |- | ||

| + | ! style="text-align:left; border-bottom: 2px solid grey" | SR1 sX | ||

| + | | colspan="6" | 100000 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="4" | - | ||

| + | | colspan="4" | 1111 | ||

| + | | style="text-align:left" | shifts register sX to the right, LSB set to 1 | ||

| + | |- | ||

| + | ! style="text-align:left" | OUTPUT sX, kk | ||

| + | | colspan="6" | 101100 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | sends register sX to I/O at address kk | ||

| + | |- | ||

| + | ! style="text-align:left" | OUTPUT sX, (sY) | ||

| + | | colspan="6" | 101101 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | sends register sX to I/O at address sY | ||

| + | |- | ||

| + | ! style="text-align:left" | STORE sX, kk | ||

| + | | colspan="6" | 101110 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | kk value | ||

| + | | style="text-align:left" | sends register sX to scratchpad at address kk | ||

| + | |- | ||

| + | ! style="text-align:left; border-bottom: 3px solid grey" | STORE sX, (sY) | ||

| + | | colspan="6" | 101111 | ||

| + | | colspan="4" | sX address | ||

| + | | colspan="8" | sY address | ||

| + | | style="text-align:left" | sends register sX to scratchpad at address sY | ||

| + | |- | ||

| + | ! style="text-align:left" | RETURN | ||

| + | | colspan="8" | 10101100 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | returns from function call | ||

| + | |- | ||

| + | ! style="text-align:left" | RETURN Z | ||

| + | | colspan="8" | 10101100 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | returns from function call if zero flag is set | ||

| + | |- | ||

| + | ! style="text-align:left" | RETURN NZ | ||

| + | | colspan="8" | 10101101 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | returns from function call if zero flag is not set | ||

| + | |- | ||

| + | ! style="text-align:left" | RETURN C | ||

| + | | colspan="8" | 10101110 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | returns from function call if carry flag is set | ||

| + | |- | ||

| + | ! style="text-align:left; border-bottom: 2px solid grey" | RETURN NC | ||

| + | | colspan="8" | 10101111 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | returns from function call if carry flag is not set | ||

|- | |- | ||

! style="text-align:left" | CALL addr | ! style="text-align:left" | CALL addr | ||

| Line 119: | Line 322: | ||

| style="text-align:left" | calls function at address if carry flag is set | | style="text-align:left" | calls function at address if carry flag is set | ||

|- | |- | ||

| − | ! style="text-align:left" | CALL NC addr | + | ! style="text-align:left; border-bottom: 2px solid grey" | CALL NC addr |

| colspan="8" | 11000111 | | colspan="8" | 11000111 | ||

| colspan="10" | program address | | colspan="10" | program address | ||

| style="text-align:left" | calls function at address if carry flag is not set | | style="text-align:left" | calls function at address if carry flag is not set | ||

| + | |- | ||

| + | ! style="text-align:left" | JUMP addr | ||

| + | | colspan="8" | 11010000 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | jumps to address | ||

| + | |- | ||

| + | ! style="text-align:left" | JUMP Z addr | ||

| + | | colspan="8" | 11010100 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | jumps to address if zero flag is set | ||

| + | |- | ||

| + | ! style="text-align:left" | JUMP NZ addr | ||

| + | | colspan="8" | 11010101 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | jumps to address if zero flag is not set | ||

| + | |- | ||

| + | ! style="text-align:left" | JUMP C addr | ||

| + | | colspan="8" | 11010110 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | jumps to address if carry flag is set | ||

| + | |- | ||

| + | ! style="text-align:left" | JUMP NC addr | ||

| + | | colspan="8" | 11010111 | ||

| + | | colspan="10" | program address | ||

| + | | style="text-align:left" | jumps to address if carry flag is not set | ||

|} | |} | ||

Revision as of 13:08, 31 October 2016

|

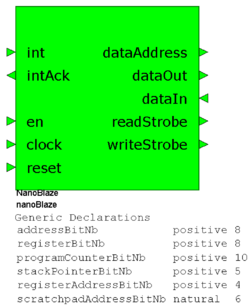

Component

The NanoBlaze is a grow-up of the Xilinx PicoBlaze microcontroller, hence the name. Various sizes can be defined with the help of generic parameters:

registerBitNbdefines the data bit widthprogramCounterBitNballows to cope with different program lengthsstackPointerBitNbadapts to various nesting depths of the subroutinesregisterBitNbdefines the data bit widthregisterAddressBitNballows to choose the number of internal registersscratchPadAddressBitNballows to manage the size of the scratchpadaddressBitNbdefines the size of the I/O space

With scratchPadAddressBitNb = 0, the scratchpad is not implemented.

The NanoBlaze's instruction ROM is designed to be mapped as a Block RAM.

Contrarily to the PicoBlaze, the NanoBlaze performs every instruction within a single clock cycle. Due to the mapping of the instruction ROM into a Block RAM, the instructions are provided delayed by one clock period compared to the program counter. With this, when a branch condition is met, the processor will anyway receive the instruction of the next memory location. Obviously, this instruction will not be executed, but this means that every successful branch requires two clock cycles.

Assembler

It has an assembler written in PERL which runs on any operating system. With this, the assembler can easily be integrated in the Mentor HDL Designer environment.

The VHDL processor code includes a disassembler process which writes the current instruction in the form of a string.

This string can be displayed in the simulator for debugging purpose.

The corresponding VHDL code is commented out for synthesis via the pragma translate_off clause.

Instruction set

The following table shows the instruction set for an 8 bit processor with 16 registers and 10 program address bits:

| instruction | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | function |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| LOAD sX, kk | 000000 | sX address | kk value | loads constant kk into register sX | |||||||||||||||

| LOAD sX, (sY) | 000001 | sX address | sY address | loads register sY into register sX | |||||||||||||||

| INPUT sX, kk | 000100 | sX address | kk value | loads I/O value at address kk to register sX | |||||||||||||||

| INPUT sX, (sY) | 000101 | sX address | sY address | loads I/O value at address sY to register sX | |||||||||||||||

| FETCH sX, kk | 000110 | sX address | kk value | loads scratchpad value at address kk to register sX | |||||||||||||||

| FETCH sX, (sY) | 000111 | sX address | sY address | loads scratchpad value at address sY to register sX | |||||||||||||||

| AND sX, kk | 001010 | sX address | kk value | applies bitwise AND of constant kk pattern to register sX | |||||||||||||||

| AND sX, sY | 001011 | sX address | sY address | applies bitwise AND of register sY pattern to register sX | |||||||||||||||

| OR sX, kk | 001100 | sX address | kk value | applies bitwise OR of constant kk pattern to register sX | |||||||||||||||

| OR sX, sY | 001101 | sX address | sY address | applies bitwise OR of register sY pattern to register sX | |||||||||||||||

| XOR sX, kk | 001110 | sX address | kk value | applies bitwise XOR of constant kk pattern to register sX | |||||||||||||||

| XOR sX, sY | 001111 | sX address | sY address | applies bitwise XOR of register sY pattern to register sX | |||||||||||||||

| TEST sX, kk | 010010 | sX address | kk value | applies bitwise AND between constant kk and register sX, only updates C and Z flags | |||||||||||||||

| TEST sX, sY | 010011 | sX address | sY address | applies bitwise AND between register sY and register sX, only updates C and Z flags | |||||||||||||||

| COMPARE sX, kk | 010100 | sX address | kk value | subtracts constant kk from register sX, only updates C and Z flags | |||||||||||||||

| COMPARE sX, sY | 010101 | sX address | sY address | subtracts register sY from register sX, only updates C and Z flags | |||||||||||||||

| ADD sX, kk | 011000 | sX address | kk value | adds constant kk to register sX | |||||||||||||||

| ADD sX, sY | 011001 | sX address | sY address | adds register sY to register sX | |||||||||||||||

| ADDCY sX, kk | 011010 | sX address | kk value | adds constant kk and carry bit to register sX | |||||||||||||||

| ADDCY sX, sY | 011011 | sX address | sY address | adds register sY and carry bit to register sX | |||||||||||||||

| SUB sX, kk | 011100 | sX address | kk value | subtracts constant kk from register sX | |||||||||||||||

| SUB sX, sY | 011101 | sX address | sY address | subtracts register sY from register sX | |||||||||||||||

| SUBCY sX, kk | 011110 | sX address | kk value | subtracts constant kk and carry bit from register sX | |||||||||||||||

| SUBCY sX, sY | 011111 | sX address | sY address | subtracts register sY and carry bit from register sX | |||||||||||||||

| SLA sX | 100000 | sX address | - | 0000 | shifts register sX to the left, C flag goes to LSB | ||||||||||||||

| RL sX | 100000 | sX address | - | 0010 | rotates register sX to the left, LSB goes to LSB | ||||||||||||||

| SLX sX | 100000 | sX address | - | 0100 | shifts register sX to the left, LSB remains in LSB | ||||||||||||||

| SL0 sX | 100000 | sX address | - | 0110 | shifts register sX to the left, LSB set to 0 | ||||||||||||||

| SL1 sX | 100000 | sX address | - | 0111 | shifts register sX to the left, LSB set to 1 | ||||||||||||||

| SRA sX | 100000 | sX address | - | 1000 | shifts register sX to the right, C flag goes to MSB | ||||||||||||||

| SRX sX | 100000 | sX address | - | 1010 | shift register sX to the right, MSB remains in MSB | ||||||||||||||

| RR sX | 100000 | sX address | - | 1100 | rotates register sX to the right, LSB goes to MSB | ||||||||||||||

| SR0 sX | 100000 | sX address | - | 1110 | shifts register sX to the right, LSB set to 0 | ||||||||||||||

| SR1 sX | 100000 | sX address | - | 1111 | shifts register sX to the right, LSB set to 1 | ||||||||||||||

| OUTPUT sX, kk | 101100 | sX address | kk value | sends register sX to I/O at address kk | |||||||||||||||

| OUTPUT sX, (sY) | 101101 | sX address | sY address | sends register sX to I/O at address sY | |||||||||||||||

| STORE sX, kk | 101110 | sX address | kk value | sends register sX to scratchpad at address kk | |||||||||||||||

| STORE sX, (sY) | 101111 | sX address | sY address | sends register sX to scratchpad at address sY | |||||||||||||||

| RETURN | 10101100 | program address | returns from function call | ||||||||||||||||

| RETURN Z | 10101100 | program address | returns from function call if zero flag is set | ||||||||||||||||

| RETURN NZ | 10101101 | program address | returns from function call if zero flag is not set | ||||||||||||||||

| RETURN C | 10101110 | program address | returns from function call if carry flag is set | ||||||||||||||||

| RETURN NC | 10101111 | program address | returns from function call if carry flag is not set | ||||||||||||||||

| CALL addr | 11000000 | program address | calls function at address | ||||||||||||||||

| CALL Z addr | 11000100 | program address | calls function at address if zero flag is set | ||||||||||||||||

| CALL NZ addr | 11000101 | program address | calls function at address if zero flag is not set | ||||||||||||||||

| CALL C addr | 11000110 | program address | calls function at address if carry flag is set | ||||||||||||||||

| CALL NC addr | 11000111 | program address | calls function at address if carry flag is not set | ||||||||||||||||

| JUMP addr | 11010000 | program address | jumps to address | ||||||||||||||||

| JUMP Z addr | 11010100 | program address | jumps to address if zero flag is set | ||||||||||||||||

| JUMP NZ addr | 11010101 | program address | jumps to address if zero flag is not set | ||||||||||||||||

| JUMP C addr | 11010110 | program address | jumps to address if carry flag is set | ||||||||||||||||

| JUMP NC addr | 11010111 | program address | jumps to address if carry flag is not set | ||||||||||||||||

Sources

This IP is found in the HEVs EDA Repository: svn: https://repos.hevs.ch/svn/eda/