SEm/labore/04 synthese

| Line 1: | Line 1: | ||

{{TOC right}} | {{TOC right}} | ||

| − | |||

= Automatische Synthese = | = Automatische Synthese = | ||

== Einleitung == | == Einleitung == | ||

| − | Dieses Labor zeigt die automatische Synthese | + | Dieses Labor zeigt die automatische Synthese von VHDL-Code. |

| − | Es basiert auf dem Beispiel des Funktionsgenerators. Die Zusammensetzung von zwei | + | Es basiert auf dem Beispiel des [[SEm/labore/01_generator|Funktionsgenerators]]. |

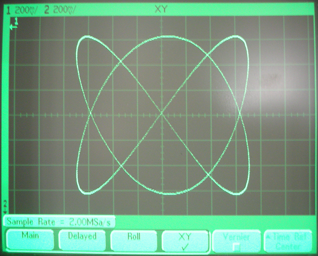

| − | Sinuswellen erlaubt es | + | Die Zusammensetzung von zwei verschiedenen Sinuswellen erlaubt es Lissajous-Figuren zu zeichnen. |

| − | + | [[Image:SEm_lissajou.png|center|Lissajous-Figur]] | |

| − | |||

== Synthese == | == Synthese == | ||

| − | + | [[Image:SEm_FPGA_sineGen.png|thumb|Zu erstellende Schaltung]] | |

| − | + | ||

| − | + | Auf das obersten Level der zu erstellenden Schaltung kommen die Ein- / Ausgangsblöcke. | |

| − | + | Hier findet man z.B. Polaritätsadapter, Tri-State-Puffer, Synchronisationslogik, ... | |

| − | + | In unserem Beispiel werden wir zwei Sinusgeneratoren, zwei Sigma-Delta-Modulatoren und eine Synchronisationslogik für das Reset-Signal setzten. | |

| − | + | Wir werden auch den Viereck-Ausgang eines der Generatoren verwenden um ein Synchronisationssignal für das Oszilloskop zu erstellen. | |

| − | Wir werden auch den Viereck-Ausgang eines der | + | |

| − | Synchronisationssignal | + | |

| − | Die Schaltung befindet sich in der Library '''Board''', die Testbank in der | + | Die Schaltung befindet sich in der Library '''Board''', die Testbank in der Library '''SineInterpolator_test'''. |

| − | Library '''SineInterpolator_test'''. | + | |

=== Schaltung === | === Schaltung === | ||

| − | + | {{TaskBox|Öffnen Sie den Block '''FPGA_sineGen''' in der Library '''Board''', kompilieren Sie ihn und überprüfen Sie per Simulation ob die Schaltung in Ordnung ist.}} | |

| − | '''Board''', kompilieren Sie ihn und | + | |

| − | Ordnung ist. | + | |

| − | Eine Simulation der Schaltung | + | Eine Simulation der Schaltung auf diesem Level erlaubt es die Funktionalität des Systems sicherzustellen. |

| − | sicherzustellen. | + | |

=== Erstellung der Datei === | === Erstellung der Datei === | ||

| − | Bestimmen Sie den Namen der generierten Datei mit dem Befehl '''Options | + | {{TaskBox|Bestimmen Sie den Namen der generierten Datei mit dem Befehl '''Options -> Main... -> User variables: concat_file = sineGen'''.}} |

| − | + | ||

| − | Starten Sie | + | {{TaskBox|Starten Sie den Task '''Prepare for synthesis'''.}} |

=== Synthese === | === Synthese === | ||

| − | Starten Sie | + | {{TaskBox|Starten Sie den Task '''Xilinx Project Navigator'''.}} |

| − | Geben Sie den Schaltugstyp an, '''xc3s500E''', und geben Sie dessen | + | {{TaskBox|Geben Sie den Schaltugstyp an, '''xc3s500E''', und geben Sie dessen Parameter, '''FG320-5'''.}} |

| − | Parameter, '''FG320-5'''. | + | |

| − | + | {{TaskBox|Fügen Sie Sie die erzeugte VHDL Datei '''sineGen.vhd''' zum Projekt hinzu.}} | |

| − | + | ||

| − | + | ||

| − | + | {{TaskBox|Stellen Sie sicher, dass '''FPGA_sineGen-struct''' die ausgewählte Schaltung ist.}} | |

| − | + | {{TaskBox|Fügen Sie Sie die Datei '''sineGen.ucf''' zum Projekt hinzu.}} | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | Finden Sie die maximale Taktfrequenz, die | + | {{TaskBox|Starten Sie den Befehl '''Synthesize - XST'''.}} |

| + | |||

| + | {{TaskBox|Prüfen Sie alle Warnungen ("'''warning'''") und stellen Sie sicher, dass die Schaltung keine Realisierungsprobleme aufweist.}} | ||

| + | |||

| + | {{TaskBox|Überprüfen Sie die Grösse der resultierenden Schaltung.}} | ||

| + | |||

| + | {{TaskBox|Finden Sie die maximale Taktfrequenz, die für diese Schaltung möglich ist.}} | ||

=== Place und Route === | === Place und Route === | ||

| − | Starten Sie das Befehl '''Implement Design'''. | + | {{TaskBox|Starten Sie das Befehl '''Implement Design'''.}} |

=== Konfiguration === | === Konfiguration === | ||

| − | + | {{TaskBox|Speisen Sie das FPGA-Board und schliessen Sie das JTAG-Downloadkabel an.}} | |

| − | Starten Sie die Befehle '''Generate Programming File''' und | + | {{TaskBox|Starten Sie die Befehle '''Generate Programming File''' und '''Configure Target Device'''.}} |

| − | '''Configure Target Device'''. | + | |

| − | + | {{TaskBox|Laden Sie die Konfiguration ins FPGA.}} | |

=== Tests === | === Tests === | ||

| − | + | {{TaskBox|Dimensionieren Sie einen passiven RLC-Tiefpassfilter, um eine Schnittfrequenz von 20 kHz zu erhalten.}} | |

| − | 20 kHz zu erhalten. | + | |

| − | Schalten Sie die Tiefpassfilter | + | {{TaskBox| |

| − | auf dem Oszilloskop. Stellen Sie | + | Schalten Sie die Tiefpassfilter an den Ausgang der Modulatoren. |

| − | + | Prüfen Sie die Sinuswellen auf dem Oszilloskop. | |

| + | Stellen Sie den Display auf X-Y Modus ein: Sie sollten nun die Lissajous-Figur sehen.}} | ||

{{navNamed|left=SEm/labore/03_konverter|left_name=03 Digital / Analog Wandler|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labore/05_amba|right_name=05 AMBA-Bus basiertes System}} | {{navNamed|left=SEm/labore/03_konverter|left_name=03 Digital / Analog Wandler|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labore/05_amba|right_name=05 AMBA-Bus basiertes System}} | ||

[[Category:SEm]] | [[Category:SEm]] | ||

Revision as of 19:07, 11 June 2013

|

Automatische Synthese

Einleitung

Dieses Labor zeigt die automatische Synthese von VHDL-Code.

Es basiert auf dem Beispiel des Funktionsgenerators. Die Zusammensetzung von zwei verschiedenen Sinuswellen erlaubt es Lissajous-Figuren zu zeichnen.

Synthese

Auf das obersten Level der zu erstellenden Schaltung kommen die Ein- / Ausgangsblöcke. Hier findet man z.B. Polaritätsadapter, Tri-State-Puffer, Synchronisationslogik, ...

In unserem Beispiel werden wir zwei Sinusgeneratoren, zwei Sigma-Delta-Modulatoren und eine Synchronisationslogik für das Reset-Signal setzten.

Wir werden auch den Viereck-Ausgang eines der Generatoren verwenden um ein Synchronisationssignal für das Oszilloskop zu erstellen.

Die Schaltung befindet sich in der Library Board, die Testbank in der Library SineInterpolator_test.

Schaltung

Eine Simulation der Schaltung auf diesem Level erlaubt es die Funktionalität des Systems sicherzustellen.

Erstellung der Datei

Synthese

Place und Route

Konfiguration

Tests

Navigation

![]() 03 Digital / Analog Wandler

03 Digital / Analog Wandler

![]() Anleitung auf Deutsch

05 AMBA-Bus basiertes System

Anleitung auf Deutsch

05 AMBA-Bus basiertes System ![]()