Inverter/laboratoire/04 hardware test 1

(Created page with "{{TOC right}} = Synthèse = Au niveau supérieur du circuit à synthétiser, il faut prévoir la circuiterie d'entrée/sortie. C'est à ce niveau que se mettent les adapta...") |

Silvan.zahno (Talk | contribs) (→Configuration) |

||

| (7 intermediate revisions by 2 users not shown) | |||

| Line 4: | Line 4: | ||

Au niveau supérieur du circuit à synthétiser, il faut prévoir la circuiterie d'entrée/sortie. C'est à ce niveau que se mettent les adaptateurs de polarité des signaux, les "buffers" haute impédance, la logique de synchronisation, ... | Au niveau supérieur du circuit à synthétiser, il faut prévoir la circuiterie d'entrée/sortie. C'est à ce niveau que se mettent les adaptateurs de polarité des signaux, les "buffers" haute impédance, la logique de synchronisation, ... | ||

| − | Dans notre exemple, nous utiliserons | + | |

| − | * notre | + | Dans notre exemple, nous utiliserons: |

| + | * notre générateur de sinus avec modulation PWM | ||

* un diviseur de fréquence qui génère la commande de comptage pour le modulateur PWM | * un diviseur de fréquence qui génère la commande de comptage pour le modulateur PWM | ||

* un diviseur de fréquence qui génère la commande d'échantillonnage | * un diviseur de fréquence qui génère la commande d'échantillonnage | ||

| Line 20: | Line 21: | ||

== Génération == | == Génération == | ||

{{TaskBox|content= | {{TaskBox|content= | ||

| − | Lancer la commande '''Prepare for synthesis'''.}} | + | # Selectioner le bloc '''FPGA_inverterControl'''. |

| + | # Lancer la commande '''Prepare for synthesis'''.}} | ||

| + | |||

| + | == Start programme Xilinx ISE == | ||

| + | {{TaskBox|content= | ||

| + | # Selectioner le bloc '''FPGA_inverterControl'''. | ||

| + | # Lancer la commande '''Xilinx Project Navigator'''.}} | ||

== Synthèse, placement et routage == | == Synthèse, placement et routage == | ||

{{TaskBox|content= | {{TaskBox|content= | ||

| − | # | + | # Dans le programme Xilinx ISE lancer la commande '''Generate Programming File''' |

| − | + | .}} | |

| − | + | == Configuration == | |

{{TaskBox|content= | {{TaskBox|content= | ||

# Alimenter le circuit FPGA et le connecter au câble de téléchargement JTAG. | # Alimenter le circuit FPGA et le connecter au câble de téléchargement JTAG. | ||

| − | # Lancer les commandes | + | # Lancer les commandes '''Configure Target Device'''. |

# Télécharger le fichier de configuration dans la FPGA.}} | # Télécharger le fichier de configuration dans la FPGA.}} | ||

| − | + | = Tests = | |

| + | |||

{{TaskBox|content= | {{TaskBox|content= | ||

| + | Vérifier: | ||

| + | * la forme du signal sinusoïdal à l'aide du PCB avec les deux filtres passe- bas | ||

| + | * le non-recouvrement des phases}} | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Brancher les PCBs du pont en H et du filtre passe-bas. | ||

| + | |||

Examiner indépendamment la forme des deux sorties du pont en H sur l'oscilloscope. | Examiner indépendamment la forme des deux sorties du pont en H sur l'oscilloscope. | ||

| − | Veiller à ne pas court-circuiter une des sorties du pont en H à la masse de l'oscilloscope.}} | + | '''Veiller à ne pas court-circuiter une des sorties du pont en H à la masse de l'oscilloscope'''.}} |

| + | |||

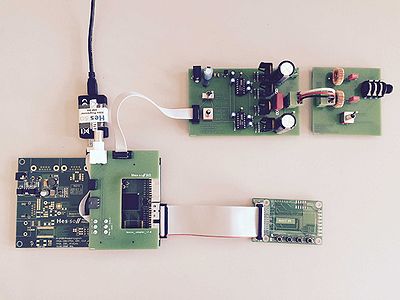

| + | [[File:Inverter boards.JPG|400px|center]] | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Brancher le PCB du transformateur et examiner la forme de la tension générée. | ||

| + | '''Couper l'alimentation pour faire les branchements et veiller à ne pas toucher à la partie du secondaire: les tensions dépassent 100 V !'''}} | ||

| + | |||

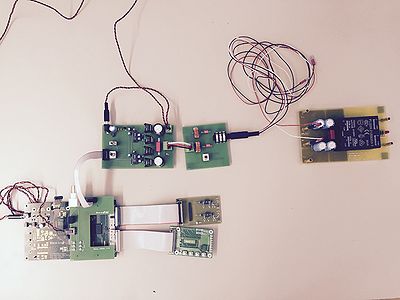

| + | [[File:Inverter boards with transfo.JPG|400px|center]] | ||

{{navNamed | {{navNamed | ||

Latest revision as of 14:50, 16 December 2019

|

Synthèse

Au niveau supérieur du circuit à synthétiser, il faut prévoir la circuiterie d'entrée/sortie. C'est à ce niveau que se mettent les adaptateurs de polarité des signaux, les "buffers" haute impédance, la logique de synchronisation, ...

Dans notre exemple, nous utiliserons:

- notre générateur de sinus avec modulation PWM

- un diviseur de fréquence qui génère la commande de comptage pour le modulateur PWM

- un diviseur de fréquence qui génère la commande d'échantillonnage

- une logique de synchronisation pour le signal de remise à zéro au démarrage.

Trois circuits de division par deux sont associés à trois des boutons de la plaque de commande: ils ne sont pas utilisés ici. Les sorties de test sont dirigées sur les diodes lumineuses de la plaque de commande.

Circuit

Ouvrir le bloc FPGA_inverterControl de la librairie Board, le compiler et vérifier que le schéma est fonctionnel.

Génération

Start programme Xilinx ISE

Synthèse, placement et routage

Configuration

- Alimenter le circuit FPGA et le connecter au câble de téléchargement JTAG.

- Lancer les commandes Configure Target Device.

- Télécharger le fichier de configuration dans la FPGA.

Tests

Vérifier:

- la forme du signal sinusoïdal à l'aide du PCB avec les deux filtres passe- bas

- le non-recouvrement des phases

Brancher les PCBs du pont en H et du filtre passe-bas.

Examiner indépendamment la forme des deux sorties du pont en H sur l'oscilloscope. Veiller à ne pas court-circuiter une des sorties du pont en H à la masse de l'oscilloscope.

Brancher le PCB du transformateur et examiner la forme de la tension générée. Couper l'alimentation pour faire les branchements et veiller à ne pas toucher à la partie du secondaire: les tensions dépassent 100 V !

Navigation

![]() 03 Temps mort des commandes de commutation

03 Temps mort des commandes de commutation

![]() Travaux de laboratoire

05 PWM à 3 niveaux

Travaux de laboratoire

05 PWM à 3 niveaux ![]()