SEm/labore/05 amba

(→AHB-Lite) |

|||

| (4 intermediate revisions by one user not shown) | |||

| Line 3: | Line 3: | ||

= AMBA-Bus basiertes System = | = AMBA-Bus basiertes System = | ||

| − | == | + | == Einleitung == |

| − | + | In diesem Labor werden wir einen simplen Peripheriebaustein für den [[Media:AMBA_AHB-Lite_spec.pdf|AMBA-Lite-Bus]] erstellen: eine bidirektionellen Ein-/Ausgangskanal. | |

| − | AHB-Lite ist eine | + | AHB-Lite ist eine einfache Variante der Busfamilie [http://www.arm.com/products/system-ip/amba-specifications.php Advanced Microcontroller Bus Architecture (AMBA)]. Sein spezielles Merkmal ist, dass er nur einen Master zulässt. |

| + | |||

| + | In einem Peripheriebaustein müssen die Werte, welche der Master (hier Mikroprozessor) in die Register schreibt, gespeichert werden. | ||

| + | Im Gegensatz werden die Werte, welche der Master liest, direkt kombinatorisch weitergegeben, ohne sie durch Flipflops zu verzögern. | ||

| + | |||

| + | === AMBA-Buszugriffe === | ||

Zugriffe erfolgen jeweils in zwei Taktzyklen, wobei der erste für die Adressierung und der zweiter zum den Datentranfser dienen. | Zugriffe erfolgen jeweils in zwei Taktzyklen, wobei der erste für die Adressierung und der zweiter zum den Datentranfser dienen. | ||

| − | == | + | {{TaskBox|content=Führen Sie eine Simualtion der Testbank <code>ahbGpio_tb</code> mit der Simulationskonfiguration <code>abhGpio.do</code> durch.}} |

| + | |||

| + | {{TaskBox|content=Beobachten Sie die Signale | ||

| + | * <code>haddr</code> | ||

| + | * <code>htrans</code> | ||

| + | * <code>hsel</code> | ||

| + | * <code>hwrite</code> | ||

| + | * <code>hwdata</code> | ||

| + | * <code>hrdata</code>}} | ||

| + | |||

| + | == Spezifikation == | ||

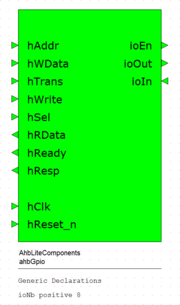

[[File:AhbLiteComponents_ahbGpio_symbol.PNG|thumb|AhbLiteComponents ahbGpio]] | [[File:AhbLiteComponents_ahbGpio_symbol.PNG|thumb|AhbLiteComponents ahbGpio]] | ||

| Line 25: | Line 40: | ||

;Leseregister | ;Leseregister | ||

: 00, Datenregister, stellt die Werte der Eingänge zur Verfügung | : 00, Datenregister, stellt die Werte der Eingänge zur Verfügung | ||

| + | |||

| + | === Design === | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Zeichnen Sie das Blockdiagram des AHB-Lite Komponenten <code>ahbGpio</code>. | ||

| + | }} | ||

=== Realisierung === | === Realisierung === | ||

| − | {{TaskBox|content=Schreiben Sie den VHDL-Code des AHB-Lite Komponenten <code>ahbGpio</code>.}} | + | {{TaskBox|content= |

| + | Schreiben Sie den VHDL-Code des AHB-Lite Komponenten <code>ahbGpio</code>. | ||

| + | }} | ||

| + | |||

| + | === Verifikation === | ||

| − | {{TaskBox|content=Führen Sie eine Simulation des Systems durch | + | {{TaskBox|content= |

| + | Führen Sie eine Simulation des Systems mit Hilfer der zur verfügung gestellten Testbank durch. Verifizieren Sie die korrekte Funktionalität des neuen Komponenten. | ||

| + | }} | ||

| − | {{navNamed|left=SEm/labore/04_synthese|left_name=04 Automatische Synthese|up=SEm/labore|up_name=Anleitung auf Deutsch|right= | + | {{navNamed|left=SEm/labore/04_synthese|left_name=04 Automatische Synthese|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labore/06_uart|right_name=UART-Peripheriebaustein}} |

[[Category:SEm]] | [[Category:SEm]] | ||

Latest revision as of 14:55, 17 April 2015

|

AMBA-Bus basiertes System

Einleitung

In diesem Labor werden wir einen simplen Peripheriebaustein für den AMBA-Lite-Bus erstellen: eine bidirektionellen Ein-/Ausgangskanal.

AHB-Lite ist eine einfache Variante der Busfamilie Advanced Microcontroller Bus Architecture (AMBA). Sein spezielles Merkmal ist, dass er nur einen Master zulässt.

In einem Peripheriebaustein müssen die Werte, welche der Master (hier Mikroprozessor) in die Register schreibt, gespeichert werden. Im Gegensatz werden die Werte, welche der Master liest, direkt kombinatorisch weitergegeben, ohne sie durch Flipflops zu verzögern.

AMBA-Buszugriffe

Zugriffe erfolgen jeweils in zwei Taktzyklen, wobei der erste für die Adressierung und der zweiter zum den Datentranfser dienen.

Spezifikation

Der zu erstellende Komponent wird dazu dienen, auf der Testplatte Schalter zu lesen und LEDs zu steuern. Die Anzahl Ein- und Ausgänge wird über den Generic ioNb gesetzt. Der Zugriff erfolgt über 3 Register.

Registerplan

- Schreiberegister

- 00, Datenregister, erhält die Werte, welche auf die Ausgänge geschrieben werden

- 01, Ausgabefreigaberegister, bestimmt die Richtung der Ein-/Ausgänge:'1' = Ausgang.

- Leseregister

- 00, Datenregister, stellt die Werte der Eingänge zur Verfügung

Design

Realisierung

Verifikation

Navigation

![]() 04 Automatische Synthese

04 Automatische Synthese

![]() Anleitung auf Deutsch

UART-Peripheriebaustein

Anleitung auf Deutsch

UART-Peripheriebaustein ![]()