SEm/labore/03 konverter

(→VHDL Code) |

|||

| (11 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{TOC right}} | {{TOC right}} | ||

| − | |||

= Digital / Analog Wandler = | = Digital / Analog Wandler = | ||

== Einleitung == | == Einleitung == | ||

| − | + | In diesem Labor werden die Kenntnisse über die Behandlung von Zahlen konsolidiert. | |

| − | Zahlen | + | Es wird uns einen nützlichen Bestandteil für die weiteren Labore liefern: den Digital / Analog Wandler (Digital / Analog Converter, DAC). |

| − | Digital / Analog Wandler. | + | Ausserdem wirft es bestimmte Fragen hinsichtlich der Simulation von Schaltungen durchschnittlicher Komplexität auf. |

| − | + | ||

| − | Die Digital / Analog Wandlung wird auf Basis eines | + | Die Digital / Analog Wandlung wird auf Basis eines Sigma-Delta (S?, SD) Modulators erstellt. |

| − | Modulators erstellt. Das Originalsignal wird | + | Das Originalsignal wird durch Impulse kodiert, deren Frequenz um einiges höher als die minimale Abtastrate ist. |

| − | + | Diese Impulskodierung ist der Pulsweitenmodulation (Pulse Width Modulation, PWM) ähnlich, da das Originalsignal sich im Mittelwert der Impulse wiederfindet. | |

| − | + | Bei gleichen Arbeitsfrequenzen liefert die SD-Codierung ein besseres Signal-Rausch-Verhältnis als die PWM. | |

| − | + | ||

| − | Arbeitsfrequenzen liefert die SD-Codierung ein besseres Signal- | + | [[Image:SEm_DAC.png|center|Delta-Sigma-Modulator]] |

| − | PWM. | + | |

== Modulator erster Ordnung == | == Modulator erster Ordnung == | ||

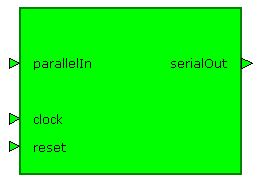

| − | + | [[Image:SEm_sigmaDelta1.png|thumb|Sigma-Delta Modulator erster Ordnung]] | |

| − | + | ||

| − | + | Der SD-Modulator erhält ein paralleles Digitalsignal und wandelt es in ein 1-Bit-Signal in der Form einer Impulsdichte um. | |

| − | + | Der SD-Modulator erster Ordnung lässt sich mit der Messung eines Wasserlaufs verdeutlichen: | |

| − | Der SD-Modulator erster Ordnung | + | |

| − | Wasserlaufs: | + | |

| − | * Der Wasserlauf wird in | + | * Der Wasserlauf wird in ein Becken geführt, welches er füllen wird. |

| − | * Sobald | + | * Sobald die Wasserhöhe eine Referenzlinie überschreitet wird ein Eimer voller Wasser aus dem Becken herausgeschöpft. |

| − | * Der | + | * Der durchschnittliche Durchfluss des Wasserlaufs entspricht somit dem Volumen des Eimers multipliziert mit der Anzahl der Eimer, die pro Zeiteinheit ausgeschöpft werden. |

Der Modulator wird wie folgt erstellt: | Der Modulator wird wie folgt erstellt: | ||

| − | * Bei jeder Taktperiode wird der neue Eingangswert einem Akkumulator | + | * Bei jeder Taktperiode wird der neue Eingangswert einem Akkumulator hinzuaddiert. |

| − | * | + | * Das MSB des Resultates ist das Ausgangssignal des Modulators (Impuls oder nicht). |

| − | * Ist dieses MSB gleich '1', so wird der Wert 2 | + | * Ist dieses MSB gleich '1', so wird der Wert 2<sup>n</sup> dem Akkumulator abgezogen, wo n gleich die Anzahl Bits des zu modulierenden Signals ist. |

| − | + | Die Schaltung befindet sich in der Library '''Beamer''', die Testbank in der Library '''Beamer_test'''. | |

| − | + | ||

| − | + | ||

| − | Die Schaltung befindet sich in der Library '''Beamer''', die Testbank in der | + | |

| − | Library '''Beamer_test'''. | + | |

=== VHDL Code === | === VHDL Code === | ||

| − | + | Der interne Akkumulator braucht mehr Bits als das Eingangssignal. | |

| + | Für den Anfang arbeiten wir mit 4 zusätzlichen Bits. | ||

| − | + | {{TaskBox|content= | |

| − | + | Schreiben Sie die VHDL Architektur des SD-Modulators.}} | |

| − | + | ||

=== Simulation === | === Simulation === | ||

| − | + | {{TaskBox|content= | |

| − | + | Kompilieren Sie und simulieren Sie den block '''DAC_tb'''.}} | |

| − | + | ||

| − | Die | + | Die Amplitude des Ausgangssignals ist durch dessen Mittelwert gegeben. |

| − | ist | + | |

| − | + | ||

| − | + | ||

| − | Untersuchen Sie den zeitlichen Verlauf des Inhalts des Akkumulators | + | {{TaskBox|content= |

| − | die notwendige Anzahl an Bits. Reduzieren Sie Anzahl der Bits des Akkumulators und | + | Finden Sie einen Weg um das parallele Eingangssignal mit der Ausgangs-Impulsdichte zu vergleichen.}} |

| − | Sie die Simulation wieder durch. | + | |

| + | Die analoge Wiederherstellung eines Signals, welches lange Zeit auf '1' oder auf '0' bleibt ist schwer zu bewerkstelligen. | ||

| + | Diese Problem kann vermieden werden, indem man den Bereich des Signals reduziert. | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Reduzieren Sie das Signal um einen Faktor von 1/2 zentrieren Sie wieder mit einer Verschiebung nach oben. | ||

| + | Führen Sie die Simulation mit dieser Änderung wieder durch.}} | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Untersuchen Sie den zeitlichen Verlauf des Inhalts des Akkumulators und bestimmen Sie die minimal notwendige Anzahl an Bits.}} | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Reduzieren Sie Anzahl der Bits des Akkumulators und führen Sie die Simulation wieder durch.}} | ||

== Modulator zweiter Ordnung == | == Modulator zweiter Ordnung == | ||

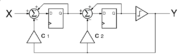

| − | + | [[Image:SEm_sigmaDelta2.png|thumb|Sigma-Delta Modulator zweiter Ordnung]] | |

| − | + | ||

| − | + | Der Modulator zweiter Ordnung enthält zwei Akkumulatoren. Die Abbildung zeigt die zu erstellenden Schaltung. | |

| − | + | Bei dieser Schaltung werden die Zahlen als vorzeichenbehaftet (signed) angesehen. | |

| − | Bei dieser Schaltung werden die Zahlen als vorzeichenbehaftet | + | |

Ist der Ausgang des zweiten Akkumulators positiv, so: | Ist der Ausgang des zweiten Akkumulators positiv, so: | ||

* ist der Ausgang gleich '1', | * ist der Ausgang gleich '1', | ||

| − | * wird ein Wert von '''c<sub>1</sub>=2<sup>nBits-1</sup>''' dem ersten Akkumulator | + | * wird ein Wert von '''c<sub>1</sub>=2<sup>nBits-1</sup>''' dem ersten Akkumulator abgezogen, |

| − | * wird ein Wert von '''c<sub>2</sub>=2<sup>nBits+3</sup>''' dem zweiten Akkumulator | + | * wird ein Wert von '''c<sub>2</sub>=2<sup>nBits+3</sup>''' dem zweiten Akkumulator abgezogen. |

Ist der Ausgang des zweiten Akkumulators negativ, so: | Ist der Ausgang des zweiten Akkumulators negativ, so: | ||

* ist der Ausgang gleich '0', | * ist der Ausgang gleich '0', | ||

| − | * wird ein Wert von '''c<sub>1</sub>=2<sup>nBits-1</sup>''' dem ersten Akkumulator | + | * wird ein Wert von '''c<sub>1</sub>=2<sup>nBits-1</sup>''' dem ersten Akkumulator hinzuaddiert, |

| − | * wird ein Wert von '''c<sub>2</sub>=2<sup>nBits+3</sup>''' dem zweiten Akkumulator | + | * wird ein Wert von '''c<sub>2</sub>=2<sup>nBits+3</sup>''' dem zweiten Akkumulator hinzuaddiert. |

| + | |||

| + | Der Wert '''nBits''' ist die Anzahl Bits des Modulatoreingangs, '''x'''. | ||

=== VHDL Code === | === VHDL Code === | ||

| − | + | Sehen Sie 8 zusätzliche Bits für jeden Akkumulator vor. | |

| − | + | Invertieren Sie das höchstwertige Bit des Eingangssignals und wenden Sie dazu noch einen Faktor von 7/8 an. | |

| − | + | {{TaskBox|content= | |

| − | + | Schreiben Sie eine zweite VHDL Architektur für den SD-Modulator.}} | |

=== Simulation === | === Simulation === | ||

| − | + | {{TaskBox|content= | |

| − | die Form des Ausgangssignals. | + | Kompilieren und simulieren Sie den block '''DAC_tb''' neu. |

| + | Prüfen Sie die Form des Ausgangssignals.}} | ||

| − | Reduzieren Sie Anzahl Bits beider | + | {{TaskBox|content= |

| − | Modulators | + | Reduzieren Sie Anzahl Bits beider Akkumulatore und stellen Sie sicher, dass die Funktion des Modulators unverändert bleibt.}} |

{{navNamed|left=SEm/labore/02_interpolation|left_name=02 Funktionsgenerator mit Interpolationsberechnung|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labore/04_synthese|right_name=04 Automatische Synthese}} | {{navNamed|left=SEm/labore/02_interpolation|left_name=02 Funktionsgenerator mit Interpolationsberechnung|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labore/04_synthese|right_name=04 Automatische Synthese}} | ||

| − | [[Category:SEm]] | + | [[Category:Bachelor]][[Category:SEm]][[Category:Deutsch]] |

Latest revision as of 16:40, 22 February 2021

|

Digital / Analog Wandler

Einleitung

In diesem Labor werden die Kenntnisse über die Behandlung von Zahlen konsolidiert. Es wird uns einen nützlichen Bestandteil für die weiteren Labore liefern: den Digital / Analog Wandler (Digital / Analog Converter, DAC). Ausserdem wirft es bestimmte Fragen hinsichtlich der Simulation von Schaltungen durchschnittlicher Komplexität auf.

Die Digital / Analog Wandlung wird auf Basis eines Sigma-Delta (S?, SD) Modulators erstellt. Das Originalsignal wird durch Impulse kodiert, deren Frequenz um einiges höher als die minimale Abtastrate ist. Diese Impulskodierung ist der Pulsweitenmodulation (Pulse Width Modulation, PWM) ähnlich, da das Originalsignal sich im Mittelwert der Impulse wiederfindet. Bei gleichen Arbeitsfrequenzen liefert die SD-Codierung ein besseres Signal-Rausch-Verhältnis als die PWM.

Modulator erster Ordnung

Der SD-Modulator erhält ein paralleles Digitalsignal und wandelt es in ein 1-Bit-Signal in der Form einer Impulsdichte um.

Der SD-Modulator erster Ordnung lässt sich mit der Messung eines Wasserlaufs verdeutlichen:

- Der Wasserlauf wird in ein Becken geführt, welches er füllen wird.

- Sobald die Wasserhöhe eine Referenzlinie überschreitet wird ein Eimer voller Wasser aus dem Becken herausgeschöpft.

- Der durchschnittliche Durchfluss des Wasserlaufs entspricht somit dem Volumen des Eimers multipliziert mit der Anzahl der Eimer, die pro Zeiteinheit ausgeschöpft werden.

Der Modulator wird wie folgt erstellt:

- Bei jeder Taktperiode wird der neue Eingangswert einem Akkumulator hinzuaddiert.

- Das MSB des Resultates ist das Ausgangssignal des Modulators (Impuls oder nicht).

- Ist dieses MSB gleich '1', so wird der Wert 2n dem Akkumulator abgezogen, wo n gleich die Anzahl Bits des zu modulierenden Signals ist.

Die Schaltung befindet sich in der Library Beamer, die Testbank in der Library Beamer_test.

VHDL Code

Der interne Akkumulator braucht mehr Bits als das Eingangssignal. Für den Anfang arbeiten wir mit 4 zusätzlichen Bits.

Simulation

Die Amplitude des Ausgangssignals ist durch dessen Mittelwert gegeben.

Die analoge Wiederherstellung eines Signals, welches lange Zeit auf '1' oder auf '0' bleibt ist schwer zu bewerkstelligen. Diese Problem kann vermieden werden, indem man den Bereich des Signals reduziert.

Modulator zweiter Ordnung

Der Modulator zweiter Ordnung enthält zwei Akkumulatoren. Die Abbildung zeigt die zu erstellenden Schaltung.

Bei dieser Schaltung werden die Zahlen als vorzeichenbehaftet (signed) angesehen.

Ist der Ausgang des zweiten Akkumulators positiv, so:

- ist der Ausgang gleich '1',

- wird ein Wert von c1=2nBits-1 dem ersten Akkumulator abgezogen,

- wird ein Wert von c2=2nBits+3 dem zweiten Akkumulator abgezogen.

Ist der Ausgang des zweiten Akkumulators negativ, so:

- ist der Ausgang gleich '0',

- wird ein Wert von c1=2nBits-1 dem ersten Akkumulator hinzuaddiert,

- wird ein Wert von c2=2nBits+3 dem zweiten Akkumulator hinzuaddiert.

Der Wert nBits ist die Anzahl Bits des Modulatoreingangs, x.

VHDL Code

Sehen Sie 8 zusätzliche Bits für jeden Akkumulator vor.

Invertieren Sie das höchstwertige Bit des Eingangssignals und wenden Sie dazu noch einen Faktor von 7/8 an.

Simulation

Navigation

![]() 02 Funktionsgenerator mit Interpolationsberechnung

02 Funktionsgenerator mit Interpolationsberechnung

![]() Anleitung auf Deutsch

04 Automatische Synthese

Anleitung auf Deutsch

04 Automatische Synthese ![]()