SEm/labore/05 amba

(→Erstellung des AHB-Lite Komponenten) |

(→AHB-Lite) |

||

| Line 5: | Line 5: | ||

== AHB-Lite == | == AHB-Lite == | ||

| − | Der Advanced High-performance Bus (AHB) ist ein Busprotokoll der [http://www.arm.com/products/system-ip/amba-specifications.php Advanced Microcontroller Bus Architecture (AMBA)], welche von [http://arm.com ARM] veröffentlicht wird. | + | Der Advanced High-performance Bus (AHB) ist ein Busprotokoll der [http://www.arm.com/products/system-ip/amba-specifications.php Advanced Microcontroller Bus Architecture (AMBA)], welche von [http://arm.com ARM] veröffentlicht wird. AHB ist ein multiplexiertes Multimasterbussystem, welches auch breite Datenbusse (bis 1024 bit) zulässt. Es wird in SoC-Systemen verwendet um verschiedene Komponenten zu verbinden, z.B. ARM-Prozessoren mit Peripheriegeräten. |

| − | AHB ist ein multiplexiertes Multimasterbussystem, welches auch breite Datenbusse (bis 1024 bit) zulässt. Es wird in SoC-Systemen verwendet um verschiedene Komponenten zu verbinden, z.B. ARM-Prozessoren mit Peripheriegeräten. | + | |

| − | AHB-Lite ist eine vereinfachte Untermenge von AHB welche nur einen Master zulässt | + | AHB-Lite ist eine vereinfachte Untermenge von AHB welche nur einen Master zulässt ([[Media:AMBA_AHB-Lite_spec.pdf|Specification]]). |

| − | + | ||

| − | [[Media:AMBA_AHB-Lite_spec.pdf|Specification]] | + | Zugriffe erfolgen jeweils in zwei Taktzyklen, wobei der erste für die Adressierung und der zweiter zum den Datentranfser dienen. |

== Erstellung des AHB-Lite Komponenten == | == Erstellung des AHB-Lite Komponenten == | ||

Revision as of 10:37, 12 March 2015

|

AMBA-Bus basiertes System

AHB-Lite

Der Advanced High-performance Bus (AHB) ist ein Busprotokoll der Advanced Microcontroller Bus Architecture (AMBA), welche von ARM veröffentlicht wird. AHB ist ein multiplexiertes Multimasterbussystem, welches auch breite Datenbusse (bis 1024 bit) zulässt. Es wird in SoC-Systemen verwendet um verschiedene Komponenten zu verbinden, z.B. ARM-Prozessoren mit Peripheriegeräten.

AHB-Lite ist eine vereinfachte Untermenge von AHB welche nur einen Master zulässt (Specification).

Zugriffe erfolgen jeweils in zwei Taktzyklen, wobei der erste für die Adressierung und der zweiter zum den Datentranfser dienen.

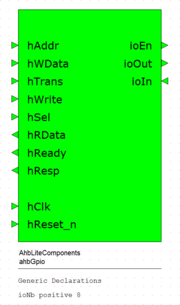

Erstellung des AHB-Lite Komponenten

Der zu erstellende Komponent wird dazu dienen, auf der Testplatte Schalter zu lesen und LEDs zu steuern. Die Anzahl Ein- und Ausgänge wird über den Generic ioNb gesetzt. Der Zugriff erfolgt über 3 Register.

Registerplan

- Schreiberegister

- 00, Datenregister, erhält die Werte, welche auf die Ausgänge geschrieben werden

- 01, Ausgabefreigaberegister, bestimmt die Richtung der Ein-/Ausgänge:'1' = Ausgang.

- Leseregister

- 00, Datenregister, stellt die Werte der Eingänge zur Verfügung

Realisierung

Navigation

![]() 04 Automatische Synthese

04 Automatische Synthese

![]() Anleitung auf Deutsch

TBC

Anleitung auf Deutsch

TBC ![]()