SEm/labore/05 amba

(→Simulation des Systems) |

|||

| Line 84: | Line 84: | ||

== Simulation des Systems == | == Simulation des Systems == | ||

| − | Um | + | Um das System zu testen wollen wir es auf eine Testbank setzen und es durch den AHB UART steuern. |

| − | UART steuern. | + | |

=== Testbench-Library === | === Testbench-Library === | ||

| − | Verlassen Sie | + | Verlassen Sie das Programm ''HDL-Designer''. |

| − | Erstellen Sie das | + | {{TaskBox|content= |

| − | '''U:\SEm_labs\Ambarchitect\ambarchitect_test'''. | + | Erstellen Sie das Verzeichnis '''U:\SEm_labs\Ambarchitect\ambarchitect_test'''.}} |

| − | + | {{TaskBox|content= | |

| − | + | Benennen Sie die Datei '''U:\SEm_labs\Ambarchitect\ambarchitect.hdp''' um in '''U:\SEm_labs\Ambarchitect\beamer.hdp'''.}} | |

| − | + | In der .hdp Datei speichert ''HDL-Designer'' den Namen und den Pfad aller Libraries Ihres Projekts. Dabei wird ein eigener Pfad für jeden Task (HDL, HDS, ModelSim, Synthese, ...) gesetzt. Die Pfade eines Tasks sind jeweils zusammen gruppiert. | |

| − | + | {{TaskBox|content= | |

| − | + | Editieren Sie '''U:\SEm_labs\Ambarchitect\beamer.hdp''' mit Ihrem Lieblingstexteditor: | |

| + | # Setzen Sie zusätzliche Referenzen zur Library '''ambarchitect_test''' (Vergleichen Sie mit '''ambarchitect'''). | ||

| + | # In der Gruppe '''ModelSim''' ändern Sie den Basispfad '''$HDS_PROJECT_DIR''' zu '''D:/Labs/SEm/Ambarchitect'''.}} | ||

| − | + | {{TaskBox|content= | |

| − | '''U:\SEm_labs\Ambarchitect\beamer.hdp'''. | + | Starten Sie ''HDL-Designer'' mit der Datei '''U:\SEm_labs\Ambarchitect\beamer.hdp'''.}} |

=== Einkapslung der Schaltung === | === Einkapslung der Schaltung === | ||

| − | + | [[Image:SEm_ambaEncapsulated.png|thumb|Eingekapselte Schaltung]] | |

| − | + | ||

| − | + | ||

| − | + | {{TaskBox|content= | |

| − | + | In ''HDL-Designer'' kopieren Sie das Modul '''ambarchitect/toplevel''' unter den Namen '''ambarchitect/gr_beamer'''.}} | |

| − | ''' | + | |

| − | + | ||

| − | + | So wird [http://ambadraw.hevs.ch AMBAdraw] diese Datei nicht überschreiben, falls Sie das Projekt neu generieren. | |

| − | + | wird. | |

| − | + | ||

| − | ''' | + | {{TaskBox|content= |

| + | # Erstellen Sie einen neuen Block '''ambarchitect/beamer'''. | ||

| + | # Erstellen Sie ein neues Blockdiagramm für diesen Block. | ||

| + | # Fügen Sie den Block '''gr_beamer''' in dieses Blockdiagramm ein. | ||

| + | # Addieren sie Blöcke mit VHDL-Code, welcher die Strukturen der GRLib Ein- und Ausgänge in einfache '''std_ulogic'''- oder '''std_ulogic_vector''' umwandelt.}} | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Schliessen Sie '''dbgo(0)''' an '''dbgi1''' an, sowie '''dbgo1''' an '''dbgi(0)''', um den Prozessor mit der DSU zu steuern.}} | ||

| − | |||

=== Testbank === | === Testbank === | ||

| − | + | [[Image:SEm_ambaTestbench.png|thumb|Testbank]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | {{TaskBox|content= | |

| − | + | # In der Library '''ambarchitect_test''', erstellen Sie eine Testbank namens '''beamer_tb'''. | |

| − | ''' | + | # Legen Sie dort hinein den Block '''ambarchitect/beamer''' |

| − | ''' | + | # Erstellen sie einem Stimuli-Generator '''beamer_tester'''.}} |

| − | + | ||

| − | Um | + | {{TaskBox|content= |

| − | ''' | + | # Um ein VHDL-Modell der Speicher, Flash und SDRAM, zu haben, kopieren Sie den Inhalt des Verzeichnisses '''R:\Modules\SI\223_SEm\Digital\Ambarchitect\ambarchitect_test''' nach '''U:\SEm_labs\Ambarchitect\ambarchitect_test'''. |

| − | + | # In HDL-Designer aktualisieren Sie die Library '''ambarchitect_test''' mit der Taste '''F5'''.}} | |

| − | + | Die VHDL-Modelle der Speicherblöcke sollten nun in ''HDL-Designer'' sichtbar sein. | |

| + | {{TaskBox|content= | ||

| + | Um einige Komponente der GRLib-Library kompilieren zu können, öffnen Sie die Library '''unisim''', selektieren Sie alle '''RAMB4*'''-Komponente und kompilieren Sie diese.}} | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Platzieren Sie diese Speicher am zu testenden System. Regeln Sie folgende Parameter: | ||

* die SDRAM hat 12 Adressbits, | * die SDRAM hat 12 Adressbits, | ||

* die 2 Bits DQM der SDRAM sind angeschlossen an sdDQM(4) und sdDQM(0), | * die 2 Bits DQM der SDRAM sind angeschlossen an sdDQM(4) und sdDQM(0), | ||

* das Signal CKE der SDRAM ist angeschlossen an sdCkE(0), | * das Signal CKE der SDRAM ist angeschlossen an sdCkE(0), | ||

* das Signal Cs_n der SDRAM ist angeschlossen an sdCS_n(0), | * das Signal Cs_n der SDRAM ist angeschlossen an sdCS_n(0), | ||

| − | * auf dem Flash sind Byte_n = '1' | + | * auf dem Flash sind Byte_n = '1' und RP_n = '1', |

| − | * auf dem Flash ist CE = "00" & | + | * auf dem Flash ist CE = "00" & RomS_n(0), |

| − | * für den Speicher-Kontroller soll bWidth = "01", | + | * für den Speicher-Kontroller soll bWidth = "01" sein, |

| − | * Für die zwei Speicher, geben sie den Link auf der kopierten Dateien in '''U:\SEm_labs\Ambarchitect\ambarchitect_test'''. | + | * Für die zwei Speicher, geben sie den Link auf der kopierten Dateien in '''U:\SEm_labs\Ambarchitect\ambarchitect_test'''.}} |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | {{TaskBox|content= | |

| − | + | Erstellen Sie einen Block, welcher den bidirektionellen Bus der Speicher auf die unidirektionellen Busse der GRLib anschliesst.}} | |

| − | * Power-on-Reset | + | {{TaskBox|content= |

| − | * die Steuerung des Systems via RS232 durch den Block '''ahbuart'''. | + | Schreiben Sie den Code der Testbank um folgende Signale zu erzeugen: |

| + | * Power-on-Reset und Taktsignal, | ||

| + | * die Steuerung des Systems via RS232 durch den Block '''ahbuart'''.}} | ||

=== Simulation === | === Simulation === | ||

Revision as of 23:13, 18 June 2013

|

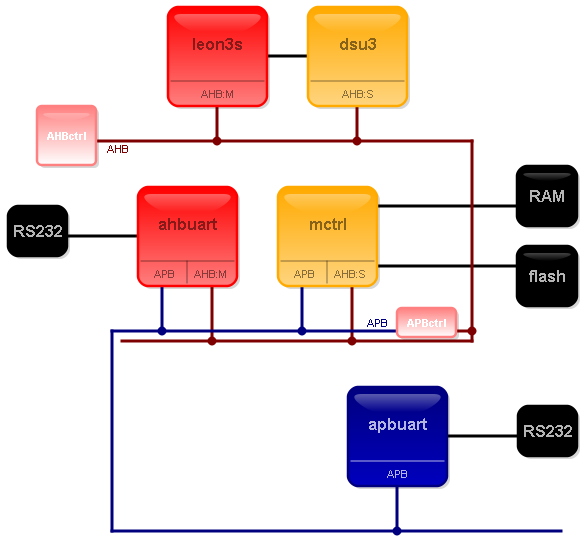

AMBA-Bus basiertes System

Einleitung

Dieses Labor zeigt die Erstellung eines AMBA Bussystem basierend auf der GRLib.

Es wird uns erlauben, eine einfache Schaltung mit einem Prozessor, einem Speicher-Interface und einer seriellen Schnittstelle zu bilden.

Zeichnung der Schaltung

Vorbereitung

Dies wird eine Referenzschaltung in AMBAdraw laden welche alle existierenden GRLib Blöcke enthält Ihre schlussendliche Schaltung wird ein Teil dieser Gesamtschaltung sein.

Schaltung

Das Manual grLib cores user manual.pdf beschreibt alle Blöcke des Systems. Mit ihm können Sie auch bestimmen, auf welche Busse (AHB oder ABP) die Komponenten angeschlossen werden.

Parametrisierung des Systems

Die Datei configuration.xls dient dazu, einige Parameter des Systems zu anzugeben.

Index

Alle Komponenten auf dem AHB-Bus haben einen eigenen Index, unabhängig vom Index des APB-Busses.

Speicherplan

Die Systemkomponente haben alle ihre eigene Speicherposition. Die GRLib parametrisiert diese mit Hilfe einer Adresse und einer Maske.

Für die AHB-Bus Slaves:

- ist die Basisadresse durch die 12 MSBs des Adresssignals gegeben

- ist die Länge des zugeteilten Speichers durch die Maske auf diese 12 MSBs gegeben.

Für die APB-Komponenten werden Basisadresse und Länge ähnlich definiert, nur aber auf den 12 weiteren Bits der Adresse.

{{TaskBox|Füllen Sie in der Datei configuration.xls die Tabellen memory map, definition und aktualisieren Sie die haddr-, hmask-, paddr- und pmask-Parameter der Komponenten in AMBAdraw.}

Komponentenspezifische Parameter

Erstellung des VHDL Codes

AMBAdraw erstellt Ihre Schaltung indem es die nicht ausgewählten Komponenten aus der Referenzschaltung entfernt.

Erstellung des anwendungsspezifischen Systems

Betrachtung des Systems

Simulation des Systems

Um das System zu testen wollen wir es auf eine Testbank setzen und es durch den AHB UART steuern.

Testbench-Library

Verlassen Sie das Programm HDL-Designer.

In der .hdp Datei speichert HDL-Designer den Namen und den Pfad aller Libraries Ihres Projekts. Dabei wird ein eigener Pfad für jeden Task (HDL, HDS, ModelSim, Synthese, ...) gesetzt. Die Pfade eines Tasks sind jeweils zusammen gruppiert.

Einkapslung der Schaltung

So wird AMBAdraw diese Datei nicht überschreiben, falls Sie das Projekt neu generieren. wird.

Testbank

Die VHDL-Modelle der Speicherblöcke sollten nun in HDL-Designer sichtbar sein.

Simulation

Initialisieren Sie die Schaltung, indem Sie den Charakter 55 h auf der RS232-Linie sendet. Der Block ahbuart kann sich damit automatisch der Baudrate der seriellen Linie anpassen.

Lesen Sie den Inhalt des Speicher an Adresse 8000.0100 h. Dies wird mit Hilfe der Sequenz 83 80 00 01 00 durchgeführt. Folgen Sie das, was auf dem AMBA-Buss passiert, von dem Empfang der Steuerung bis zum Zurücksenden der Daten. ErkLären Sie den Wert der Daten, welche vom Speicher gelesen wurden.

Figure 5. Simulation

File:AmbaSimulation.png

Schreiben Sie den Code der Testbank , um folgende Signale zu erzeugen:

- Power-on-Reset un Taktsignal,

- die Steuerung des Systems via RS232 durch den Block ahbuart.

Simulation

Initialisieren Sie die Schaltung, indem Sie den Charakter 55 h auf der RS232-Linie sendet. Der Block ahbuart kann sich damit automatisch der Baudrate der seriellen Linie anpassen.

Lesen Sie den Inhalt des Speicher an Adresse 8000.0100 h. Dies wird mit Hilfe der Sequenz 83 80 00 01 00 durchgeführt. Folgen Sie das, was auf dem AMBA-Buss passiert, von dem Empfang der Steuerung bis zum Zurücksenden der Daten. ErkLären Sie den Wert der Daten, welche vom Speicher gelesen wurden.

Figure 5. Simulation

Navigation

![]() 04 Automatische Synthese

04 Automatische Synthese

![]() Anleitung auf Deutsch

06 APB Komponent

Anleitung auf Deutsch

06 APB Komponent ![]()