SEm/labore/01 generator

|

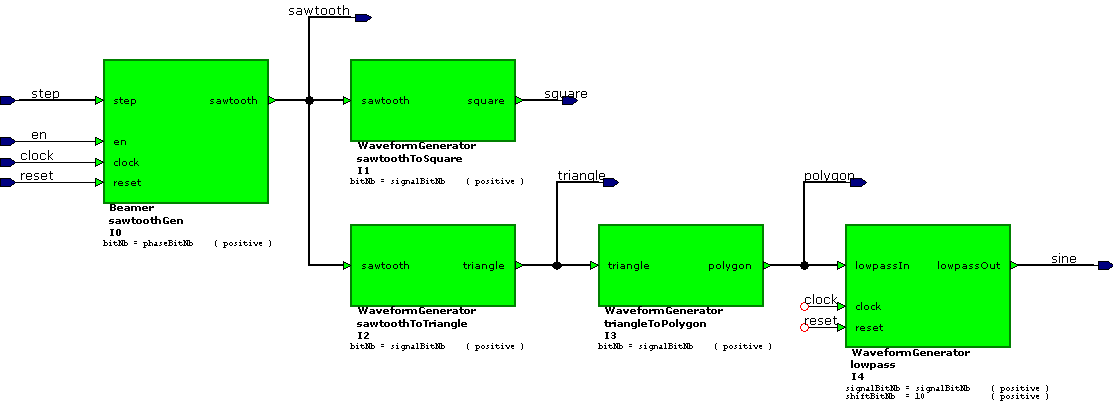

Funktionsgenerator

Einleitung

In diesem Labor werdet ihr das Schreiben von VHDL-Code für kombinatorische und sequenzielle Blöcke lernen.

Dies am Beispiel eins Funktionsgenerator welche folgende Signale erzeugt:

- ein Sägezahnsignal, sawtooth,

- ein Vierecksignal, square,

- ein Dreiecksignal, triangle,

- ein Sinuswellensignal, sine.

Alle diese Signale sind als Binärzahlen mit 16 Bits (immer positiv) dargestellt.

Die Schaltung befindet sich in der Bibliothek WaveformGenerator, die Testbank dazu in der Bibliothek WaveformGenerator_test.

Sägezahnsignalgenerator

Der Sägezahnsignalgenerator wird durch einen Zähler erstellt, welcher um und um zählt. Das Eingangssignal step erlaubt es, die Frequenz des erzeugten Sägezahnsignals zu steuern. Bei jeder steigenden Flanke des clock und wenn en = '1' addiert der Zähler den Wert von step zu seinem eigenem. Somit zählt er um so schneller je grösser der Wert von step ist.

VHDL Code

Dies ist eine synchrone sequenzielle Schaltung.

Dieser Block hat einen generischen Parameter (generic): bitNb. Dieser Parameter ist sowohl für die Entity wie auch für die zu schreibende Architektur definiert.

Aufgepasst: sawtooth ist ein Ausgangssignal und ihm kann deshalb nur ein Wert zugewiesen werden. Es ist nicht möglich, seinen Wert zurückzulesen, um ihm den Wert von step zu addieren. Deshalb muss man ein internes Signal definieren, welches gelesen und geschrieben werden kann. Am Ende wird das interne Signal auf das Ausgangssignal zugewiesen.

Simulation

Umwandlung von Sägezahn zu Viereck

Das Sägezahnsignal wird in ein Viereck umgewandelt indem nur das MSBs des Sägezahnsignals betrachtet wird. Dennoch soll das erzeugte Vierecksignal auf 16 Bit kodiert sein.

VHDL Code

Dies ist eine kombinatorische Schaltung.

Das Ausgangssignal ist eine auf 16 Bits kodierte Binärzahl.

Simulation

Umwandlung von Sägezahn zu Dreieck

Die Umwandlung vom Sägezahnsignal zum Dreiecksignal wird gemacht, indem man "den oberen Teil der Sägezahn nach unten biegt", wenn das MSB des Signals gleich '1' ist.

VHDL Code

Dies ist eine kombinatorische Schaltung.

Wenn das MSB des Sägezahnsignals gleich '1' ist, invertieren Sie alle Bits des Sägezahnsignals.

Da das MSB des erzeugten Signals immer auf '0' ist, verwendet man nur die Hälfte des zu Verfügung stehenden Bereichs. Man wird also das erhaltene Signal mit zwei multiplizieren müssen um den ganzen Bereich auszunützen. Eine Multiplikation mit 2 entspricht einer Schiebung um ein Bit nach links.

Es ist am einfachsten ein internes Signal zu definieren, das dem Resultat der ersten Operation entspricht. Dieses wird dann benutzt um den Ausgang zu erzeugen. Der Code wird auch besser lesbar, wenn das MSB des Eingangssignals als zusätzliches internes Signal definiert wird.

Simulation

Umwandlung von Dreieck zu Sinus

Die Umwandlung von Dreieck zu Sinus kann mit Hilfe einer Wahrheitstabelle (ROM) mit allen Sinuswerten erstellt werden. Diese Lösung ist zwar präzis, verbraucht aber viele Ressourcen in der programmierbaren Schaltung.

Für dieses Labor werden wir das Dreiecksignal filtern, um nur dessen Fundamentalkomponente zu behalten: eine Sinuswelle. Um die Arbeit des Tiefpassfilters zu vereinfachen, werden wir das Dreiecksignal vorerst in eine Polygonform umwandeln, welche der Sinuswelle näher steht.

VHDL Code

Die Umwandlung vom Dreieck zum Polygon fängt mit einer Multiplikation mit 1,5 an. Dies benötigt ein Signal mit einem zusätzlichem Bit. Danach werden die Spitzen des Dreiecks "abgeschnitten". Dazu werden alle Werte des Signals die kleiner sind als 1/8 des Maximalwertes durch denselben Wert von 1/8 ersetzt. Symmetrisch dazu ersetzt man alle Werte über 5/8 des Maximalwertes durch denselben Wert von 5/8. Letztlich wird das Polygonsignal um 1/8 nach unten verschoben um den Minimalwert bei 0 zu haben. Dabei ist zu beachten, dass die Werte 1/8 und 5/8 der vollen Skala (Full Scale, FS) des 17-Bit Signals und nicht der Amplitude des Dreiecksignals zu entnehmen sind.

Die Multiplikation mit 1,5 wird durch eine Schiebung und eine Addition erstellt. Das Resultat benötigt ein Bit mehr als die Originalzahl. Jedoch kann nach der Schiebung um 1/8 nach unten dieses zusätzliche Bit vernachlässigt werden und das Ausgangssignal auf derselben Anzahl an Bits wie der Eingang kodiert werden.

Die Tiefpassfilterung wird mit Hilfe eines Integrators (ein Akkumulator) mit Dämpfung erstellt. In jeder Taktperiode wird zum Akkumulatorwert der Wert des Eingangsignals hinzu addiert (Integration). Gleichzeitig wird der um eine gewisse Anzahl Bits verschobene Wert des Akkumulators subtrahiert (Dämpfung). Die Anzahl Bits der Verschiebung ergeben die Schnittfrequenz. Wird diese Zahl um 1 vergrössert, so wird die Schnittfrequenz durch 2 geteilt.

Der Akkumulator braucht gleichviel Bits wie das Eingangssignal plus die Anzahl Bits der Verschiebung. Als Ausgang sollen die MSBs des Akkumulators genommen werden.

Simulation

Navigation

![]() 00 Installation

00 Installation

![]() Anleitung auf Deutsch

02 Interpolation

Anleitung auf Deutsch

02 Interpolation ![]()