Hardware/Mezzanine/audio AD-DA

(→Input range) |

m |

||

| Line 1: | Line 1: | ||

{{TOC right}} | {{TOC right}} | ||

== Audio AD/DA mezzanine board == | == Audio AD/DA mezzanine board == | ||

| + | |||

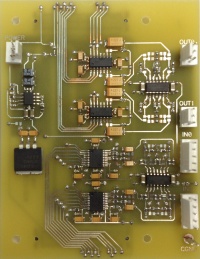

| + | [[File:FPGA_Mezza_Audio_ADDA.jpg|200px|Audio AD-DA Mezzanine]] | ||

This board has been developed as a low-cost replacement of the [[Hardware/Mezzanine/high-speed_AD-DA|high-speed AD-DA board]]. | This board has been developed as a low-cost replacement of the [[Hardware/Mezzanine/high-speed_AD-DA|high-speed AD-DA board]]. | ||

Latest revision as of 08:51, 7 November 2012

|

Audio AD/DA mezzanine board

This board has been developed as a low-cost replacement of the high-speed AD-DA board. It features:

Power supply

The supply from the connector is used to power the TL064 op amps. They can be powered between ±3.5 V and ±18V.

A TPS54227 DC/DC converter generates 6.5 V from the power supply and is followed by a 5 V regulator.

Hence, the minimal power supply range is about ±7 V.

Input range

The board input signals are brought to a first stage of differential op-amp circuits with:

- R15 = R17 = R16 = R18 = R36 = R38 = R37 = R39

- gain1 = R17 / R8 = R15 / R10 = R18 / R12 = R16 / R14 = R38 / R29 = R36 / R31 = R39 / R33 = R37 / R35

- pos_offset / pos_supply = R17 / R7 = R18 / R11 = R38 / R28 = R39 / R32

- neg_offset / neg_supply = R17 / R10 = R18 / R13 = R38 / R30 = R39 / R34

The ADC inputs range from 0 V to 5V.

The output of this first circuit is decoupled and brought to a second stage built around the in-circuit op-amp of the ADC. The gain of the second stage is:

- gain2 = R23 / R21 = R24 / R22 = R44 / R42 = R45 / R43

Output range

The DAC output signals are brought to differential op-amp circuits with:

- R15 = R17 = R16 = R18 = R36 = R38 = R37 = R39

- gain1 = R17 / R8 = R15 / R10 = R18 / R12 = R16 / R14 = R38 / R29 = R36 / R31 = R39 / R33 = R37 / R35

- pos_offset / pos_supply = R17 / R7 = R18 / R11 = R38 / R28 = R39 / R32

- neg_offset / neg_supply = R17 / R10 = R18 / R13 = R38 / R30 = R39 / R34

The DAC outputs range from 0 V to 5V.