Hardware/FPGAPoetic

(→Features) |

(→Analog to digital converters) |

||

| (11 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{TOC right}} | {{TOC right}} | ||

| − | The basic idea behind this board is to have a | + | The basic idea behind this board is to have a FPGA board that interface a VME connector compatible with the POETIC Rack backplane. |

| + | This board was developped during [https://gitlab.hevs.ch/theses/bachelor/jean-nanchen/fpga-developing-board-demonstrator Jean Nanchen's TB] (2021) and used in the NGRW project in addition with the [[Hardware/Mezzanine/Poetic|FPGA ADC-DAC Mezzanine]]. | ||

{|class=wikitable | {|class=wikitable | ||

|- | |- | ||

| − | ! Type || FPGA | + | ! Type || FPGA Poetic || Schematic || UCF || Description |

|- | |- | ||

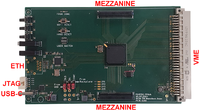

| − | | V1.0 || [[File: | + | | V1.0 || [[File:FpgaPoetic.png|200px|FPGA Poetic V1.0]] || [[Media:FPGAPoetic_v1_0_schematics.pdf|FPGA-Poetic v1.0 Schematic PDF]] || [[Media:FPGARack_v1_0.ucf|FPGA-Rack v1.0 UCF Files]] || There are different FPGA mounted: Spartan 6 XC6SLX45, Spartan 6 XC6SLX100, Spartan 6 XC6SLX150 |

|- | |- | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

= Features = | = Features = | ||

| Line 28: | Line 20: | ||

* 4 User Switches | * 4 User Switches | ||

* 3 Buttons | * 3 Buttons | ||

| − | * | + | * 100.0MHz Main Clock |

* VME connector 3x32Pin compatible with POETIC Rack backplane | * VME connector 3x32Pin compatible with POETIC Rack backplane | ||

* 2 Mezzanine Connector ARM-EBS and FPGA-EBS compatible | * 2 Mezzanine Connector ARM-EBS and FPGA-EBS compatible | ||

* Powered by USB or VME Power | * Powered by USB or VME Power | ||

| + | |||

| + | = Analog to digital converters = | ||

| + | |||

| + | The mezzanine board holds 20 [https://www.ti.com/product/ADS7886 ADS7886] analog to digital converters. | ||

| + | |||

| + | These are 12 bit converters with a maximal sampling rate of 1 MHz. | ||

| + | |||

| + | <span style="color:red">Actually Channel 6, 7, 8, 9, 10, 12, 13, 14 and 15 don't work (Probably due to propagation delay with SCLK)</span> | ||

| + | |||

| + | = Digital to analog converters = | ||

| + | |||

| + | The mezzanine board holds 2 [https://www.ti.com/product/DAC124S085 DAC124S085] quad analog to digital converters, | ||

| + | allowing for 8 analog output channels. | ||

| + | |||

| + | These are quad 12 bit converters with a maximal sampling rate of 1.8 MHz if only one channel is used. | ||

| + | The sampling rate drops to 460 kHz when all 4 channels are used. | ||

= Programmation = | = Programmation = | ||

Latest revision as of 15:50, 12 July 2022

|

The basic idea behind this board is to have a FPGA board that interface a VME connector compatible with the POETIC Rack backplane. This board was developped during Jean Nanchen's TB (2021) and used in the NGRW project in addition with the FPGA ADC-DAC Mezzanine.

| Type | FPGA Poetic | Schematic | UCF | Description |

|---|---|---|---|---|

| V1.0 |  |

FPGA-Poetic v1.0 Schematic PDF | FPGA-Rack v1.0 UCF Files | There are different FPGA mounted: Spartan 6 XC6SLX45, Spartan 6 XC6SLX100, Spartan 6 XC6SLX150 |

Features

- 1 Ethernet Port

- USB FTDI

- Spartan 6 LX45 - LX100 - LX150

- 2x4 Leds

- 4 User Switches

- 3 Buttons

- 100.0MHz Main Clock

- VME connector 3x32Pin compatible with POETIC Rack backplane

- 2 Mezzanine Connector ARM-EBS and FPGA-EBS compatible

- Powered by USB or VME Power

Analog to digital converters

The mezzanine board holds 20 ADS7886 analog to digital converters.

These are 12 bit converters with a maximal sampling rate of 1 MHz.

Actually Channel 6, 7, 8, 9, 10, 12, 13, 14 and 15 don't work (Probably due to propagation delay with SCLK)

Digital to analog converters

The mezzanine board holds 2 DAC124S085 quad analog to digital converters, allowing for 8 analog output channels.

These are quad 12 bit converters with a maximal sampling rate of 1.8 MHz if only one channel is used. The sampling rate drops to 460 kHz when all 4 channels are used.

Programmation

V1.0 is only programmable via JTAG.