Hardware/FPGAEBS

(Difference between revisions)

m |

|||

| Line 6: | Line 6: | ||

There are several versions of FPGA EBS Boards. | There are several versions of FPGA EBS Boards. | ||

| − | The [[Hardware/ | + | The [[Hardware/Stock_FPGA|stock]] can be verified and updated on-line. |

{|class=wikitable | {|class=wikitable | ||

| Line 12: | Line 12: | ||

! Type || FPGA-EBS Full board || FPGA-EBS Student board || FPGA-EBS Mezzanine || Schematic || UCF || Description | ! Type || FPGA-EBS Full board || FPGA-EBS Student board || FPGA-EBS Mezzanine || Schematic || UCF || Description | ||

|- | |- | ||

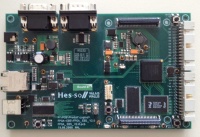

| − | | V2.1 || [[File:FPGA_Full_v2_1.jpg|200px|FPGA EBS V2.1]] [[Hardware/ | + | | V2.1 || [[File:FPGA_Full_v2_1.jpg|200px|FPGA EBS V2.1]] [[Hardware/Stock_FPGA#Full|boards 30-35]] || [[File:FPGA_Student_v2_1.jpg|200px|FPGA EBS Student Version V2.1]] [[Hardware/Stock_FPGA#Student|boards 11-13]]|| [[File:FPGA_Mezza_v2_1.jpg|115px|FPGA EBS Mezza V2.1]] [[Hardware/Stock_FPGA#Mezzanine|boards 40-41]] || [[Media:FPGA_EBS_v2_1_schematics.pdf|FPGA-EBS v2.1 Schematic PDF]] || [[Media:FPGA_EBS_v2_ucf.rar|FPGA-EBS v2.1 UCF Files]] || Improved second version of FPGA-EBS comes with Xilinx XC3S500e or XC3S1200E. Note that there is a different UCF Pin constraining file |

|- | |- | ||

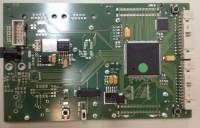

| − | | V2.0 || [[File:FPGA_Full_v2_0.jpg|200px|FPGA EBS V2.0]] [[Hardware/ | + | | V2.0 || [[File:FPGA_Full_v2_0.jpg|200px|FPGA EBS V2.0]] [[Hardware/Stock_FPGA#Full_2|boards 21-28]] || [[File:FPGA_Student_v2_0.jpg|200px|FPGA EBS Student Version V2.0]] [[Hardware/Stock_FPGA#Student_2|boards 1-8]] || Not existing ||[[Media:FPGA_EBS_v2_0_schematics.pdf|FPGA-EBS v2.0 Schematic PDF]] || [[Media:FPGA_EBS_v2_ucf.rar|FPGA-EBS v2.0 UCF Files]] || Second FPGA-EBS Version comes only with Xilinx XC3S500E |

|- | |- | ||

| V1.0 || [[File:FPGA_Full_v1_0.jpg|200px|FPGA EBS V1.0]] || [[File:FPGA_Student_v1_0.jpg|200px|FPGA EBS Student Version V1.0]] || [[File:FPGA_Mezza_v1_0.jpg|115px|FPGA EBS Mezza Version V1.0]] || [[Media:FPGA_EBS_v1_0_schematics.pdf|FPGA-EBS v1.0 Schematic PDF]] || Not available ||First FPGA-EBS Version comes with a Xilinx XC2S150 or XC2S250 FPGA. <br> '''Please note that for Spartan 2 is no longer supported by Xilinx, an ISE Version <= 9.2i has to be used''' | | V1.0 || [[File:FPGA_Full_v1_0.jpg|200px|FPGA EBS V1.0]] || [[File:FPGA_Student_v1_0.jpg|200px|FPGA EBS Student Version V1.0]] || [[File:FPGA_Mezza_v1_0.jpg|115px|FPGA EBS Mezza Version V1.0]] || [[Media:FPGA_EBS_v1_0_schematics.pdf|FPGA-EBS v1.0 Schematic PDF]] || Not available ||First FPGA-EBS Version comes with a Xilinx XC2S150 or XC2S250 FPGA. <br> '''Please note that for Spartan 2 is no longer supported by Xilinx, an ISE Version <= 9.2i has to be used''' | ||

Revision as of 09:32, 14 August 2012

|

A short description of the FPGA-EBS board is found on the ISI Project Page.

Board families

There are several versions of FPGA EBS Boards. The stock can be verified and updated on-line.

| Type | FPGA-EBS Full board | FPGA-EBS Student board | FPGA-EBS Mezzanine | Schematic | UCF | Description |

|---|---|---|---|---|---|---|

| V2.1 |  boards 30-35 boards 30-35 |

boards 11-13 boards 11-13 |

boards 40-41 boards 40-41 |

FPGA-EBS v2.1 Schematic PDF | FPGA-EBS v2.1 UCF Files | Improved second version of FPGA-EBS comes with Xilinx XC3S500e or XC3S1200E. Note that there is a different UCF Pin constraining file |

| V2.0 |  boards 21-28 boards 21-28 |

boards 1-8 boards 1-8 |

Not existing | FPGA-EBS v2.0 Schematic PDF | FPGA-EBS v2.0 UCF Files | Second FPGA-EBS Version comes only with Xilinx XC3S500E |

| V1.0 |  |

|

|

FPGA-EBS v1.0 Schematic PDF | Not available | First FPGA-EBS Version comes with a Xilinx XC2S150 or XC2S250 FPGA. Please note that for Spartan 2 is no longer supported by Xilinx, an ISE Version <= 9.2i has to be used |

A VHDL test code with the default UCF Files can be found at the EDA SVN Reopsitory

UCF Pin Differences

On the FPGA-EBS v2.X Boards, you can find two different FPGA Spartan3 Chips.

There are 3 Pin differences between Boards with XC3S500E and XC3S1200E.

| Pin Function | Pin on XC3S500E | Pin on XC3S1200E |

|---|---|---|

| ParallelPort2(16) | F4 | E6 |

| MezzanineData(9) | E17 | E3 |

| sdCke | P15 | P15 |

Other changes between FPGA-EBS V2.0 and V2.1

There are some other changes made in the Ethernet part of those boards. Several bugs were changes and corrected.

- TCT and RCT Pins of the Ethernetconnector were strapped to 3.3V, and decoupled with Capacitors (C59 & C104)

- Serial Capacitors on the RX+ and RX- lines were replaced by 0Ohm Resistors (R61 & R63)

- Proper Reset circuit for the Ethernetphy is put on place (D13, D14, R62 & C108)