Hardware/FPGAEBS

(Difference between revisions)

m |

m |

||

| Line 27: | Line 27: | ||

{|class=wikitable | {|class=wikitable | ||

| − | |- Pin Function || Pin on XC3S500E || Pin on XC3S1200E | + | |- |

| − | |- ParallelPort2(16) || F4 || E6 | + | | Pin Function || Pin on XC3S500E || Pin on XC3S1200E |

| − | |- MezzanineData(9) || E17 || E3 | + | |- |

| − | |- sdCke || P15 || P15 | + | | ParallelPort2(16) || F4 || E6 |

| + | |- | ||

| + | | MezzanineData(9) || E17 || E3 | ||

| + | |- | ||

| + | | sdCke || P15 || P15 | ||

| + | |- | ||

|} | |} | ||

Revision as of 08:16, 27 April 2012

|

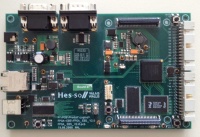

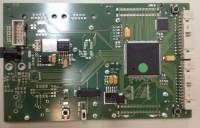

There are several Version of FPGA EBS Boards

| Type | FPGA-EBS Full board | FPGA-EBS Student board | FPGA-EBS Mezzanine | Schematic | Description |

| V2.1 |  |

|

|

FPGA-EBS v2.1 Schematic PDF | Improved second version of FPGA-EBS comes with Xilinx XC3S500e or XC3S1200E. Note that there is a different UCF Pin constraining file |

| V2.0 |  |

|

Not existing | FPGA-EBS v2.0 Schematic PDF | Second FPGA-EBS Version comes only with Xilinx XC3S500E |

| V1.0 |  |

|

|

FPGA-EBS v1.0 Schematic PDF | First FPGA-EBS Version comes with a Xilinx XC2S150 or XC2S250 FPGA. Please note that for Spartan 2 is no longer supported by Xilinx, an ISE Version <= 9.2i has to be used |

A VHDL test code with the default UCF Files can be found at:

i:\Institut\Infrastructure\Labos\A309\FPGA\VHDL\ELN_board\

UCF Pin Differences

On the FPGA-EBS v2.X Boards, you can find two different FPGA Spartan3 Chips. Pin differences between Boards with XC3S500E and XC3S1200E.

| Pin Function | Pin on XC3S500E | Pin on XC3S1200E |

| ParallelPort2(16) | F4 | E6 |

| MezzanineData(9) | E17 | E3 |

| sdCke | P15 | P15 |