Hardware/FPGARackZynqADDAV1

From UIT

|

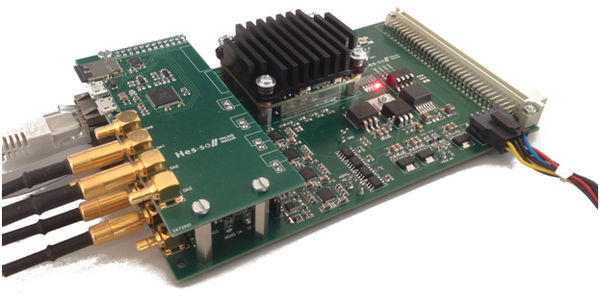

This board embeds 4 ADCs, 4 DACs and a FPGA/CPU kit. It is intended to be used for data acquisition / generation / processing. Unlike the OLGMADDA V1 board or the HiSADDA V1 board, the FPGA includes a hard-core ARM CPU (useful with a Linux and Ethernet, for example). This board was developped by pah (Charles Papon) for his master thesis.

| Type | FPGA Rack | Documentation | Description |

|---|---|---|---|

| V1.0 |  |

Link |

FPGA: Xilinx Zynq Z020 |

Core features

- Trenz Electronic TE0720 SoC module with :

- 1x FPGA XC7Z020-xCLG484x

- With hardcore ARM Cortex-A9 dual-core (unified 512Kbyte L2 Cache, 256Kbyte on-chip Memory)

- Programmable logic based on Artix-7 FPGA (85K Logic Cells, 140x36KBit BRAM Blocks (total: 560KByte), 220 DSP Slices)

- 1x 10/100/1000 Gigabit Ethernet transceiver (PHY)

- 1x USB 2.0 high speed ULPI transceiver

- 2x 256Mbitx16 DDR3 SDRAM (total: 1GByte, 32bit width)

- 1x 32Mbyte SPI FLASH memory

- 1x 4GByte e-NAND

- 3x User LEDs

- Onboard DCDC power supplies (1.0V@4.0A, 1.5V@1.5A, 1.8V@1.5A)

- 152x single ended I/Os (75x LVDS pairs possible)

- 1x FPGA XC7Z020-xCLG484x

- 4x A/D 16bits 10MSPS (Analog Devices AD7626)

- Single ended or differential depending on cable soldering

- 4x D/A 14bits 125MSPS (Texas Instruments DAC2904)

- Single ended

- 13x 3.3V digital inputs

- microSD card socket (QuadSPI)

- 6x user LEDs

- 2x user user DIL switches

- 1x JTAG Connector

- 1x microUSB - OTG interface

- 1x microUSB - 2xUART/1xJTAG bridge

- 1x DIN41612 VME Compatible Connector 3x32 pins (only HVME16, without CMOS termination)

Power supply considerations

This board is powered through the HVME backplane bus (+5V, +12V, -12V).

VME connector logic levels

The I/O bank which interfaces the VME connector is only 3.3V. Be careful with other FPGA Rack boards with 2.5V/3.3V jumper.

Known issues

The following points need to be considered when using this board version :

- Inverted polarity on DAC outputs.

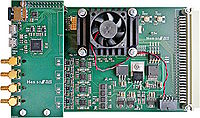

- On the TE0720 kit, the thermal dissipation is too big for the passive heatsink. An additionnal fan is required.

- On the user I/O of the TE0720 kit, pin MIO0 must be overridden to GND due to a Xilinx tools issue with the microSD card detection.

- Bad labeling on the PCB :

- Swapped "ADx" and "DAx" labels

- Swapped CH0-CH1 for the DAC.

- Swapped CH2-CH3 for the DAC.

- All testpoints (power supplies + GND) are unconnected (PCB layout issue).