Hardware/Mezzanine/Poetic

From UIT

(Difference between revisions)

(→10 ADCs, 8 DACs) |

|||

| Line 3: | Line 3: | ||

== 10 ADCs, 8 DACs == | == 10 ADCs, 8 DACs == | ||

| − | This mezzanine was developped for the FPGA Poetic Board during [https://gitlab.hevs.ch/theses/bachelor/jean-nanchen/fpga-developing-board-demonstrator Jean Nanchen's TB] (2021) and used in the NGRW project. | + | This mezzanine was developped for the FPGA Poetic Board during [https://gitlab.hevs.ch/theses/bachelor/jean-nanchen/fpga-developing-board-demonstrator Jean Nanchen's TB] (2021) and used in the NGRW project with the [[Hardware/FPGAPoetic|FPGA Poetic Board]]. |

The mezzanine board has 8 SMA connectors (DAC output), 2 connectors 2x10 pins (ADC input), 1 connector 2x5 pins (SPI LVDS) and 1 connector 2x9 pins (SPARE I/O). | The mezzanine board has 8 SMA connectors (DAC output), 2 connectors 2x10 pins (ADC input), 1 connector 2x5 pins (SPI LVDS) and 1 connector 2x9 pins (SPARE I/O). | ||

Latest revision as of 14:00, 1 October 2021

|

10 ADCs, 8 DACs

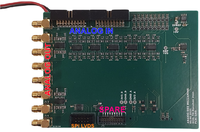

This mezzanine was developped for the FPGA Poetic Board during Jean Nanchen's TB (2021) and used in the NGRW project with the FPGA Poetic Board. The mezzanine board has 8 SMA connectors (DAC output), 2 connectors 2x10 pins (ADC input), 1 connector 2x5 pins (SPI LVDS) and 1 connector 2x9 pins (SPARE I/O).

This board is used for the EMVS students project day.

| Version | Photo | Schematic |

|---|---|---|

| V1.0 |  |

FPGA ADC DAC Mezza Schematic PDF |

ADCs

The ADS7886 is a 6 12-Bit, 1-MSPS ADC.

DACs

The DAC084S085 is a Quad 8-Bit DAC with a serial interface that is compatible with standard SPI, QSPI, MICROWIRE, and DSP interfaces.