SEm/labore/09 pipeline

(Created page with "{{TOC right}} = Pipelined Addierer = {{navNamed|left=SEm/labore/08_soc|left_name=08 Realisierung eines AMBA-SoCs|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labor...") |

|||

| Line 1: | Line 1: | ||

{{TOC right}} | {{TOC right}} | ||

| − | = | + | = Hochgeschwindigkeits-Addierer = |

| + | == Einleitung == | ||

| + | |||

| + | In diesem Labor nehmen wir das Thema des Hochgeschwindigkeits-Addierers wieder auf, diesmal mit der ''Pipeline''-Technik. | ||

| + | |||

| + | == Kombinatorischer Addierer == | ||

| + | |||

| + | Der Hochgeschwindigkeits-Addierer wird aus einer Reihe von kleineren Addierern aufgebaut. | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Öffnen Sie die Testbank <code>parallelAdder_tb</code>, schreiben Sie die VHDL-Architektur des Addieres <code>parallelAdder</code> und verifizieren Sie deren Funktionalität. | ||

| + | }} | ||

| + | |||

| + | == Iterativer Addierer == | ||

| + | |||

| + | Der Hochgeschwindigkeits-Addierer besteht aus einer Gruppe von kombinatorischen Addierern. Der iterative Addierer wird als Zwischenschritt realisiert, um zu verstehen, wie ein digitaler Schaltkreis in VHDL mit in Schleifen instanziierten Blöcken realisiert werden kann. | ||

| + | |||

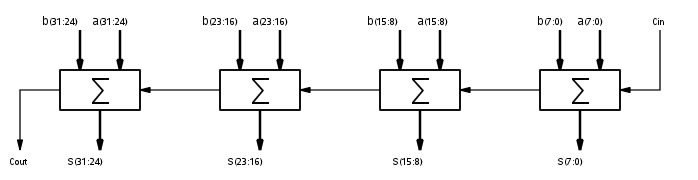

| + | [[File:Sem labs iterative adder.svg|center|Iterativer Addierer]] | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Dans la librairie <code>pipelinedOperators</code>, définir l'architecture <code>noPipe</code> | ||

| + | comme architecture par défaut du bloc <code>pipelineAdder</code>. | ||

| + | }} | ||

| + | |||

| + | L'architecture <code>noPipe</code> donne un exemple de description VHDL d'un système itératif | ||

| + | par le placement de composants à l'aide d'une boucle <code>for … generate</code>. | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Ouvrir le banc de test de l'additionneur combinatoire <code>pipelineAdder_tb</code>, | ||

| + | écrire l'architecture VHDL de l'additionneur <code>pipelineAdder</code> et vérifier le bon fonctionnement de l'additionneur. | ||

| + | }} | ||

| + | |||

| + | == Additionneur rapide == | ||

| + | |||

| + | L'additionneur rapide se fait en insérant des bascules entre les additionneurs combinatoires. | ||

| + | |||

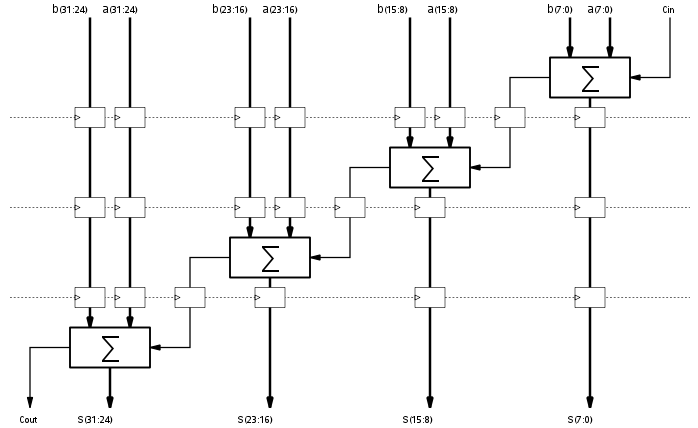

| + | [[File:Sem labs pipelined adder.svg|center|Additionneur pipeline]] | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Dans la librairie <code>pipelinedOperators</code>, définir l'architecture <code>studentVersion</code> | ||

| + | comme architecture par défaut du bloc <code>pipelineAdder</code>. | ||

| + | }} | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Ecrire l'architecture VHDL de l'additionneur <code>pipelineAdder</code> et vérifier le bon fonctionnement de l'additionneur. | ||

| + | }} | ||

| + | |||

| + | == Compteur rapide == | ||

| + | |||

| + | L'adittioneur rapide est capable de fournir une nouvelle somme à chaque période d'horloge. | ||

| + | Il lui faut cependant un certain nombre de périodes d'horloge avant de fournir le résultat de la somme. | ||

| + | |||

| + | {{TaskBox|content= | ||

| + | Expliquer comment réaliser un compteur rapide à l'aide de l'additionneur rapide. | ||

| + | }} | ||

{{navNamed|left=SEm/labore/08_soc|left_name=08 Realisierung eines AMBA-SoCs|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labore/09_pipeline|right_name=-}} | {{navNamed|left=SEm/labore/08_soc|left_name=08 Realisierung eines AMBA-SoCs|up=SEm/labore|up_name=Anleitung auf Deutsch|right=SEm/labore/09_pipeline|right_name=-}} | ||

| − | [[Category:SEm]] | + | [[Category:Bachelor]] [[Category:SEm]] [[Category:Deutsch]] |

Latest revision as of 14:47, 29 April 2016

|

Hochgeschwindigkeits-Addierer

Einleitung

In diesem Labor nehmen wir das Thema des Hochgeschwindigkeits-Addierers wieder auf, diesmal mit der Pipeline-Technik.

Kombinatorischer Addierer

Der Hochgeschwindigkeits-Addierer wird aus einer Reihe von kleineren Addierern aufgebaut.

Iterativer Addierer

Der Hochgeschwindigkeits-Addierer besteht aus einer Gruppe von kombinatorischen Addierern. Der iterative Addierer wird als Zwischenschritt realisiert, um zu verstehen, wie ein digitaler Schaltkreis in VHDL mit in Schleifen instanziierten Blöcken realisiert werden kann.

L'architecture noPipe donne un exemple de description VHDL d'un système itératif

par le placement de composants à l'aide d'une boucle for … generate.

Additionneur rapide

L'additionneur rapide se fait en insérant des bascules entre les additionneurs combinatoires.

Compteur rapide

L'adittioneur rapide est capable de fournir une nouvelle somme à chaque période d'horloge. Il lui faut cependant un certain nombre de périodes d'horloge avant de fournir le résultat de la somme.

Navigation

![]() 08 Realisierung eines AMBA-SoCs

08 Realisierung eines AMBA-SoCs

![]() Anleitung auf Deutsch

-

Anleitung auf Deutsch

- ![]()