Libero IDE presentation

|

Libero IDE is used to program the Microchip FPGAs.

Work environment

At HEI, we laucnch Libero IDE directly from HDL Designer. The setup bases on a set of environment variables.

Files

The main design files are located in $PATH/Board/concat:

$DESIGN.vhd $DESIGN.pdc

The Physical Design Constraints .pdc file specifies the I/O locations and electric levels.

Further design files are found in $PATH/Board/Libero:

$DESIGN.prjx synthesis/$DESIGN_syn.prj designer/impl1/$DESIGN.adb designer/impl1/$DESIGN.ide_des designer/impl1/$DESIGN.pdb

This second set of files is copied into a temporary directory which will be additionally populated by the numerous design files generated by the deign tool.

Tasks

Launching the tools is done in two steps.

- with the top-level block selected, the

prepare for synthesistask does the following:- the design tool generates a single VHDL file

- the

trimLibs.plscript replaces all library definitions with the one ofwork

- the

Libero Project Navigatortask does the following:- the

Update prjx.plscript updates the paths specified in the.prjxfile to reflect the project location's. - the Libero IDE is launched

- the

Interactive run of the Libero tools

To check the synthesis and downnload results wit a better accuracy, one can start Libero IDE and go through:

- Synthesize -> open interactively

- implementation option -> specify clock frequency

- run

- view log

- Compile -> open interactively

- I/O Attibute Editor

- Layout

- Programming File

- FlashPro -> open interactively

- verify programmer

- verify

.pdbbitstream file - program

Tips

PDC

To ensure the correct behavior of the project, specify ALL I/Os in your .pdc file.

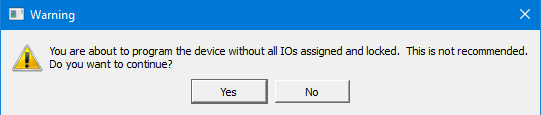

If the following window is shown when trying to configure the FPGA, stop there as one pin has been omitted and it may create undefined and unwanted problems :

Clocks

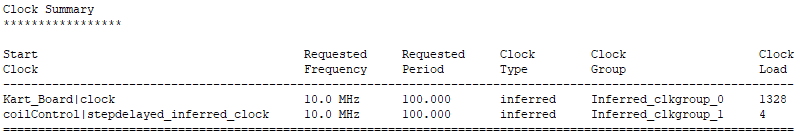

Only one clock should be found during the synthesize.

More than one will also create undefined behaviors. It can be seen in the $DESIGN.srr file, under the Clock Summary. Such, the real behavior will not reflect the simulation.

For example, in the following, a second clock is found in the block setting the coils signals:

For the record, the coils were then wrongly set, making the stepper slip and consume a lot of current.

Optimizations

Libero will optimize cloned functionalities, remove unnecessary registers ...

It may happen that a whole route is removed (e.g. in the students solutions, where the distancePulse is not used by default). If the signal is kept in the PDC, you may encounter an error that it is not found because Libero removed it internally.

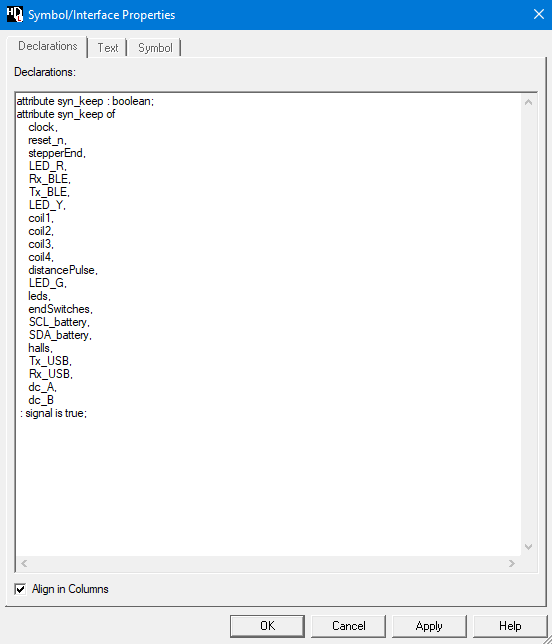

To avoid those problems, open the symbol of the Kart_Board block in HDL, then on the right click on Declarations.

There, it is possible to specify pre-defined attributes that will impact the synthesis. To keep all signals, the following is used :