SEm/laboratoires/01 generateur

|

Générateur de fonctions

Introduction

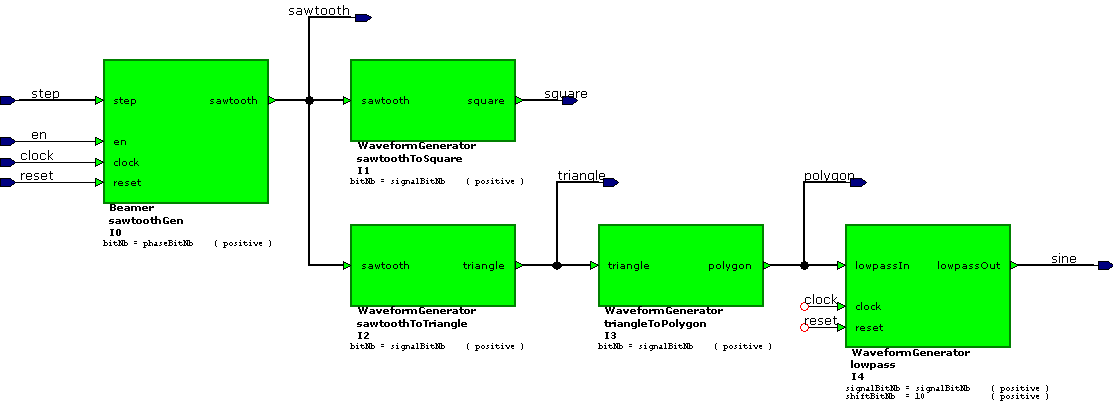

Dans ce laboratoire, nous allons illustrer l'écriture du code VHDL de blocs combinatoires et de blocs séquenciels synchrones par la réalisation d'un générateur de fonctions numérique.

Le générateur délivre

- un signal en dents de scie, sawtooth,

- un signal carré, square,

- un signal triangulaire, triangle,

- un signal sinusoïdal, sine.

Tous ces signaux sont codés en tant que nombres de 16 bits. Le circuit se trouve dans la librairie WaveformGenerator, le banc de test dans la librairie WaveformGenerator_test. Le programme de dessin de circuit est lancé à l'aide du fichier de commande sineGen.bat.

Générateur de signal en dents de scie

Le générateur de signal en dents de scie se fait à l'aide d'un compteur qui tourne en rond. Un nombre en entrée, step, permet de commander la fréquence du signal en dents de scie. A chaque flanc montant de l'horloge, lorsque en = '1, le compteur ajoute la valeur de step à sa valeur courante. Ainsi, plus la valeur de step est grande et plus le compteur tourne rapidement.

Code VHDL

Ce circuit est un circuit séquentiel synchrone.

Ce bloc contient un paramètre générique (generic): bitNb. Ce paramètre est défini aussi bien pour l'entité que pour l'architecture à écrire.

le signal de sortie, sawtooth, peut uniquement être assigné. Il ne peut être lu pour lui additionner la valeur de step. Il faut donc définir un signal interne, lequel peut être lu et assigné, et copier ce signal sur le port de sortie.

Simulation

Transformation de dents de scie à carré

La transformation du signal en dents de scie en un signal carré se fait en ne considérant que le bit de poids fort du signal en dents de scie. Cependant, le signal généré sera aussi codé sur 16 bits.

Code VHDL

Ce circuit est un circuit combinatoire. Le signal de sortie est un nombre non-signé codé sur 16 bits.

Simulation

Transformation de dents de scie à triangle

La transformation du signal en dents de scie en un signal triangulaire se fait en "repliant la dent de scie vers le bas" lorsque le bit de poids fort du signal en dents de scie vaut '1'.

Code VHDL

Ce circuit est un circuit combinatoire. Lorsque le bit de poids fort du signal en dents de scie vaut '1', inverser tous les bits du signal en dent de scie. Comme le signal généré aura ainsi toujours son bit de poids fort à '0', il n'utilise que la moitié de la gamme à disposition. Il faudra donc multiplier le signal obtenu par deux. Ceci correspond à un décalage vers la gauche. Il est indiqué de définir un signal interne résultant de la première opération de repliement et utilisé pour générer la sortie. Il est aussi plus lisible de définir un autre signal interne: le bit de poids fort du signal d'entrée.

Simulation

Transformation triangle à sinus

La transformation de triangle à sinus peut se faire par une table de vérité (ROM) qui contient toutes ces valeurs. Cette solution, même si elle est la plus précise, est très coûteuse en matériel.

Dans ce laboratoire, nous prendrons le parti de filtrer le signal triangulaire pour ne conserver que sa fondamentale: une sinus. Pour simplifier la tâche de filtrage, nous allons transformer le signal triangulaire en un signal polygonal de forme plus proche du sinus désiré.

Code VHDL

La transformation de triangle à ploygone se commence en multipliant le triangle par 1.5. Après cela, il faut remplaçer toutes les valeurs plus petites que 1/8 de la gamme du triangle obtenu par cette valeur de 1/8: on coupe ce qui est en-dessous. De même, on coupe aussi ce qui dépasse les 5/8. Finalement, on peut décaler le signal de 1/8 vers le bas.

Les valeurs 1/8 et 5/8 sont relatives à la pleine échelle (Full Scale, FS) possible du signal et non à l'amplitude maximale du triangle.

La multiplication par 1.5 se fait par un décalage et une addition. Le résultat de la multiplication nécessite un bit de plus que le signal de départ. Après le décalage vers le bas, on peut ignorer le bit de poids fort et revenir au même nombre de bits qu'à l'entrée.

Le filtrage passe-bas se fait à l'aide d'un intégrateur réalisé par un accumulateur. A chaque période d'horloge, on additionne la valeur de l'entrée au contenu de l'accumulateur (intégration), et on leur soustrait la valeur de l'accumulateur décalée d'un certain nombre de bits. Le nombre de bits de décalage donne la fréquence de coupure. A chaque incrémentation de ce nombre, la fréquence de coupure est divisée par 2.

L'accumulateur nécessite un nombre de bits égal à celui du signal d'entrée plus le nombre de bits de décalage. En sortie, il faut reprendre les bits de poids fort de l'accumulateur.

Simulation

Navigation

![]() 00 Installation

00 Installation

![]() Travaux de laboratoire

02 Générateur de fonctions avec calcul d'interpolation

Travaux de laboratoire

02 Générateur de fonctions avec calcul d'interpolation ![]()