Components/IP/SPI

|

This IP's can be found on the EDA Repository: svn: https://repos.hevs.ch/svn/eda/

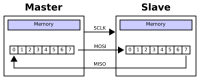

The ISI SPI Master IP Core, comes in 2 Sizes. For both blocs configuration like CPOL, CPHA can be adjusted. The SPI bloc can also be found in the template design in the library SPI.

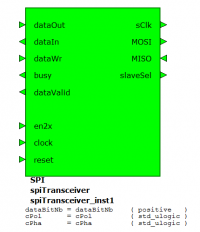

SPI Transceiver

This is a minimalistic bloc acting as Master for writing and reading SPI Data. It has a prefetch feature, which means you can fetch data before the current transmission is finished in order to continue the current access.

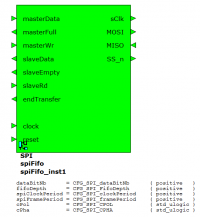

SPI FIFO

This bloc is a wrapper around the SPI Transceiver and adds several features

- Data handling with input and output FIFO.

- Single access and multiple access feature

- Definable SPI clock period

- Definable SPI Interframe gap (for Single accesses only)

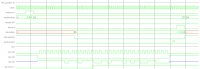

Single Access

For performing a single access the data has to be written into the master FIFO, after that you need to wait until the endTransfer signal. Once this signal is set you can read the data on the slave FIFO.

Multiple Access

For performing a multiple access, the data has to be written into the master FIFO. If the second data is written before the endTransfer signal arrives, the access will be continued until no data in the FIFO is available. In the end, the endTransfer signal has it's impulse and you have to read all the data from the FIFO.

There is a simulation screenshot for clarification.