Hardware/FPGAEBS/Configuration

From UIT

(Difference between revisions)

m (→FPGA Configuration) |

|||

| (5 intermediate revisions by one user not shown) | |||

| Line 3: | Line 3: | ||

= General = | = General = | ||

After designing and simulating your design based on [[Components/Designs/VHDL_template|VHDL Template Design]], you have to prepare it: | After designing and simulating your design based on [[Components/Designs/VHDL_template|VHDL Template Design]], you have to prepare it: | ||

| − | + | == In HDL-Designer == | |

| − | + | {{TaskBox|content=Perform Task Flow '''Prepare for Synthesis'''}} | |

| − | + | # Generates all VHDL Files | |

| − | + | # Concatenates them into a single VHDL File (<code><library>\concat\concatenated.vhd</code>) | |

| − | + | # Trims work libraries (<library>\concat\<designName>.vhd) | |

| − | + | {{TaskBox|content=Perform Task Flow '''Xilinx Project Navigator'''}} | |

| − | + | # Updates the ISE (*.xise) Project file | |

| − | + | # Launches ISE | |

| − | + | ==In ISE== | |

| − | + | {{TaskBox|content=Perform Task '''Generate Programming File'''}} | |

| − | + | # Runs Synthesis | |

| − | + | # Runs P&R | |

| − | + | # Generate Programming File *.bit | |

| + | {{TaskBox|content=Perform Task '''Configure Target Device'''}} | ||

| + | # Launches Impact | ||

After that you can either way [[Hardware/FPGAEBS/Configuration#FPGA_Configuration|download the file directly to the FPGA]] or [[Hardware/FPGAEBS/Configuration#Flash_Writing|create another file to download to the non-volatile memory]]. | After that you can either way [[Hardware/FPGAEBS/Configuration#FPGA_Configuration|download the file directly to the FPGA]] or [[Hardware/FPGAEBS/Configuration#Flash_Writing|create another file to download to the non-volatile memory]]. | ||

| Line 32: | Line 34: | ||

## Choose '''Assign new configuration file''' | ## Choose '''Assign new configuration file''' | ||

##:[[File:fpgaebs_impact_1_3.png|FPGA prog 3]] | ##:[[File:fpgaebs_impact_1_3.png|FPGA prog 3]] | ||

| − | ## Choose previously generated *.bit file | + | ## Choose previously generated *.bit file in folder <code>Xilinx</code> |

## Choose No for Attaching SPI or BPI PROM | ## Choose No for Attaching SPI or BPI PROM | ||

##:[[File:fpgaebs_impact_1_4.png|FPGA prog 4]] | ##:[[File:fpgaebs_impact_1_4.png|FPGA prog 4]] | ||

Latest revision as of 15:01, 20 January 2015

|

General

After designing and simulating your design based on VHDL Template Design, you have to prepare it:

In HDL-Designer

- Generates all VHDL Files

- Concatenates them into a single VHDL File (

<library>\concat\concatenated.vhd) - Trims work libraries (<library>\concat\<designName>.vhd)

- Updates the ISE (*.xise) Project file

- Launches ISE

In ISE

- Runs Synthesis

- Runs P&R

- Generate Programming File *.bit

- Launches Impact

After that you can either way download the file directly to the FPGA or create another file to download to the non-volatile memory.

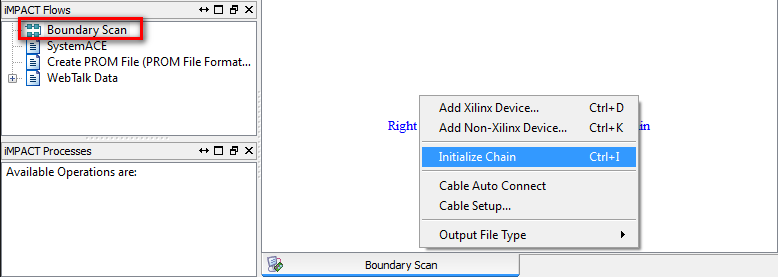

FPGA Configuration

If you want to program the FPGA directly, you can use the previously generated *.bit file.

Execute the following steps:

- Perform a boundary Scan

- Left click on the FPGA symbol (turns green)

- Right click on the FPGA

- Choose Assign new configuration file

- Choose previously generated *.bit file in folder

Xilinx - Choose No for Attaching SPI or BPI PROM

- Right click on the FPGA

- Choose Program

- Choose Verify if you like (not necessary)

- DONE

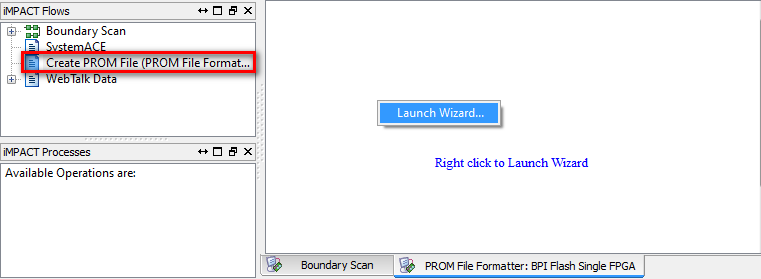

Flash Writing

To program the xcf04s Platform Flash In-System Programmable Configuration PROM you need to turn your *.bit into an *.mcs file. This file can then be used to program the Platform Flash through JTAG.

Flash programming works ONLY with Official Xilinx USB Programmer