File list

This special page shows all uploaded files. When filtered by user, only files where that user uploaded the most recent version of the file are shown.

| Name | Thumbnail | Size | User | Description | Versions | |

|---|---|---|---|---|---|---|

| 11:16, 27 February 2013 | Beckhoff FB1130 system.jpg (file) |  | 184 KB | Zas | (Beckhoff FB1130 Piggyback and Motherboard) | 1 |

| 11:15, 27 February 2013 | Beckhoff FB1130 Ref design.ucf (file) | 21 KB | Zas | (User Constraint File for Reference Design of Beckhoff for FB1130) | 1 | |

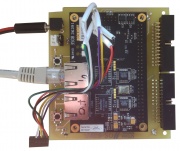

| 11:15, 27 February 2013 | Beckhoff FB1130 piggyback.jpg (file) |  | 201 KB | Zas | (Beckhoff Piggyback FB1130 Board for EtherCAT Development) | 1 |

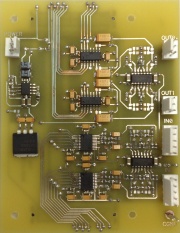

| 11:14, 27 February 2013 | Beckhoff FB1130 motherboard.jpg (file) |  | 780 KB | Zas | (Motherboard developed @ HES-SO for Beckhoff Piggyback FB1130 Board) | 1 |

| 16:00, 25 February 2013 | Actel CoreMP7 schematic.pdf (file) | 445 KB | Zas | (Schematics file fo the Actel CoreMP7 Development Kit) | 1 | |

| 15:57, 25 February 2013 | Actel CoreMP7.jpg (file) |  | 575 KB | Zas | (Actel Development Kit Core MP7) | 1 |

| 15:51, 25 February 2013 | FPGA Passive EthernetTab schematics.pdf (file) | 521 KB | Zas | (Schematics of the Passive Ethernet Tab aka. Passive Ethernet Measurement Point) | 1 | |

| 15:40, 25 February 2013 | Passive Measurement Point small.jpg (file) |  | 340 KB | Zas | (Passive Ethernet Measurement Point, used and eeveloped during Diplomaworks in Sweden) | 1 |

| 15:31, 25 February 2013 | GPS Navman Jupiter30.png (file) |  | 603 KB | Zas | (GPS receiver Module Jupiter 30) | 1 |

| 08:40, 25 February 2013 | Xilinx platform cable usb ii.jpg (file) |  | 262 KB | Zas | (Official Xilinx Platform USB Programmer) | 1 |

| 16:02, 18 February 2013 | Update mgc pkginfo.zip (file) | 519 B | Zas | (Script for let run HDL Designer < 2010 on the HESSO License Server.) | 1 | |

| 10:50, 7 February 2013 | Presentation en UITWiki.pdf (file) | 1.01 MB | Zas | (Official Presentatino of the UIT Wiki held 24.01.2012) | 1 | |

| 10:49, 24 January 2013 | FPGA Mezza ADC schematic.pdf (file) | 69 KB | Zas | (HES-SO FPGA-EBS Mezzanine ADC Extention schematic) | 2 | |

| 09:49, 22 January 2013 | ADC Cirrus CS5368.pdf (file) | 368 KB | Zas | (Datasheet of the Cirrus Logix CS5368 ADC) | 1 | |

| 10:10, 15 January 2013 | PICEBS v1 schematics.pdf (file) | 93 KB | Zas | (Schematics of the PICEBS V1 Development Board) | 2 | |

| 10:07, 15 January 2013 | PICEBS1 v1 0 doc.pdf (file) | 216 KB | Zas | (Documentation of the PICEBS V1 Development Board) | 1 | |

| 10:00, 15 January 2013 | PICEBS1 Box.jpg (file) |  | 563 KB | Zas | (HESSO PICEBS v1 Development Board in Box) | 1 |

| 10:00, 15 January 2013 | PICEBS1.jpg (file) |  | 787 KB | Zas | (HESSO PICEBS v1 Development Board) | 1 |

| 09:59, 15 January 2013 | ARMEBS3 v1 3.jpg (file) |  | 776 KB | Zas | (HESSO ARMEBS v1.3 Development Board) | 1 |

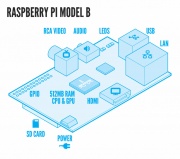

| 09:17, 15 January 2013 | RaspberryPiModelB overview.jpg (file) |  | 112 KB | Zas | (Schematic Model of the Raspberry Pi) | 1 |

| 10:05, 22 November 2012 | FPGA PP HEB lcd schematic.pdf (file) | 271 KB | Zas | (Schematic of the FPGA Parallelport extentions LCD) | 1 | |

| 10:05, 22 November 2012 | FPGA PP HEB lcd.jpg (file) |  | 110 KB | Zas | (FPGA Parallelport extention LCD) | 1 |

| 08:53, 7 November 2012 | FPGA Mezza Audio ADDA.jpg (file) |  | 775 KB | Zas | (Low Cost audio AD-DA Mezzanine Board) | 1 |

| 08:52, 7 November 2012 | FPGA Mezza Highspeed ADDA.jpg (file) |  | 476 KB | Zas | (Highspeed AD-DA Mezzanine Board used for projects IGOR and MOLIS) | 1 |

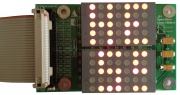

| 09:56, 8 October 2012 | FPGA PP heb matrix.jpg (file) |  | 236 KB | Zas | (FPGA Parallel Port Board HEB_MATRIX) | 1 |

| 13:14, 4 October 2012 | FPGA PP HEB Matrix schematic.pdf (file) | 74 KB | Zas | (Schematic of the HEB Matrix Led Parallel board) | 1 | |

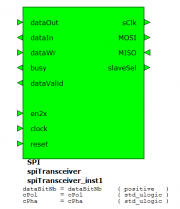

| 14:11, 1 October 2012 | SPI master transceiver.png (file) |  | 8 KB | Zas | (HDL-Designer Bloc of the SPI Transceiver) | 1 |

| 14:11, 1 October 2012 | SPI master multi access.png (file) |  | 15 KB | Zas | (Simulation of a Multiaccess for the SPI_FIFO bloc) | 1 |

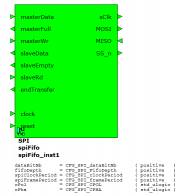

| 14:10, 1 October 2012 | SPI master FIFO.png (file) |  | 13 KB | Zas | (HDL Deisgner Bloc of the SPI_FIFO Master) | 1 |

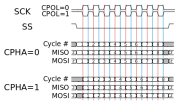

| 14:09, 1 October 2012 | SPI timing.png (file) |  | 47 KB | Zas | (SPI Timing Diagram) | 1 |

| 14:09, 1 October 2012 | SPI master slave.png (file) |  | 9 KB | Zas | (SPI Master Slave Architecture) | 1 |

| 11:13, 1 October 2012 | Microsemi logo.gif (file) | 7 KB | Zas | (Logo of Microsemi) | 1 | |

| 11:11, 1 October 2012 | Microsemi fp4 programmer.jpg (file) |  | 608 KB | Zas | (Programmer FlashPro 4 from Microsemi (Former Actel)) | 1 |

| 13:42, 14 September 2012 | FPGARack v1 0 schematics.pdf (file) | 310 KB | Zas | (Schematic of the FPGA Rack Educational Board v1.0) | 2 | |

| 08:31, 14 September 2012 | FPGARack v1 0.ucf (file) | 21 KB | Zas | (Pin Contraint File for Board FPGA Rack v1.0.) | 2 | |

| 11:38, 13 September 2012 | FPGA EBS v2 xc3s1200e.ucf (file) | 5 KB | Zas | (UCF Pin Constrain File for FPGA-EBS Board equipped with the Spartan 3 XC3S1200E Chip) | 1 | |

| 11:38, 13 September 2012 | FPGA EBS v2 xc3s500e.ucf (file) | 5 KB | Zas | (UCF Pin Constrain File for FPGA-EBS Board equipped with the Spartan 3 XC3S500E Chip) | 1 | |

| 16:13, 17 August 2012 | FPGA Mezza ADC.jpg (file) |  | 255 KB | Zas | (Reverted to version as of 14:12, 17 August 2012) | 4 |

| 16:02, 17 August 2012 | FPGA Mezza Ethernettap.jpg (file) |  | 395 KB | Zas | (Mezzanine for FPGA Board. It has 2 Ethernetconnectors and Physicals plus many debug headers.) | 1 |

| 12:07, 8 August 2012 | FPGA Mezza Ethernettap schematic.pdf (file) | 259 KB | Zas | (Schematic of the Ethertap Mezzanine extentions for FPGA-EBS and FPGA-Rack) | 1 | |

| 12:07, 12 July 2012 | Digilent xilinx programmer.jpg (file) |  | 15 KB | Zas | (Digilent Xilinx Programmer with Impact support) | 1 |

| 12:01, 12 July 2012 | Digilent logo.png (file) | 157 KB | Zas | (Digilent Logo) | 1 | |

| 11:57, 12 July 2012 | Digilent logo.gif (file) | 3 KB | Zas | (Digilent Logo) | 1 | |

| 11:32, 27 June 2012 | FPGA Rack v1 0.jpg (file) |  | 249 KB | Zas | (FPGA Rack Development Board with Spartan 6) | 1 |

| 08:57, 21 June 2012 | Fpgarack impact 2 10.png (file) |  | 20 KB | Zas | (FPGA Rack Flash programmation How-to picture 10) | 1 |

| 08:56, 21 June 2012 | Fpgarack impact 2 9.png (file) |  | 19 KB | Zas | (FPGA Rack Flash programmation How-to picture 9) | 1 |

| 08:56, 21 June 2012 | Fpgarack impact 2 8.png (file) |  | 19 KB | Zas | (FPGA Rack Flash programmation How-to picture 8) | 1 |

| 08:55, 21 June 2012 | Fpgarack impact 2 7.png (file) |  | 14 KB | Zas | (FPGA Rack Flash programmation How-to picture 7) | 1 |

| 08:55, 21 June 2012 | Fpgarack impact 2 6.png (file) |  | 18 KB | Zas | (FPGA Rack Flash programmation How-to picture 6) | 1 |

| 08:55, 21 June 2012 | Fpgarack impact 2 5.png (file) |  | 29 KB | Zas | (FPGA Rack Flash programmation How-to picture 5) | 1 |

First page |

Previous page |

Next page |

Last page |