Hardware/Parallelport/heb microphone

From UIT

Revision as of 11:59, 18 May 2018 by Francois.corthay (Talk | contribs)

|

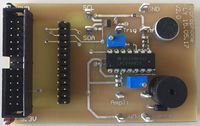

The board was designed for the SEm VHDL FSM lab.

It has a beeper which can emit a Morse code signal and a microphone for receiving it.

| Version | Photo | Schematics | Stock |

|---|---|---|---|

| V1.1 |  |

HEB-microphone Schematic PDF | 10 fully mounted |

Beeper

The beeper is driven directly by a digital I/O line.

Microphone

The microphone's output is amplified and connected to an ADC. The amplified signal is also triggered in order to deliver a simple digital input to the FPGA.

Setup

The microphone's output is quite small. It is first fed to a fixed amplifier through a passive RC highpass. The highpass has a cutoff frequency of ... Hz. The amplifier has a gain of xxx.

The trigger is a Schmitt trigger. When there is no signal, the trigger output can be as well low or high.