Components/IP/SD

(→Testbench) |

(→Sigma-Delta modulator) |

||

| Line 42: | Line 42: | ||

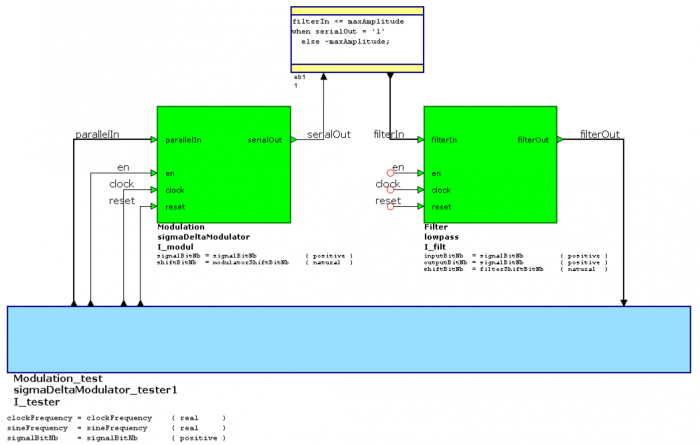

The testbench generates a sinewave input to the modulator. | The testbench generates a sinewave input to the modulator. | ||

| + | Clock and signal frequencies are defined as constants in the top-level architecture and passed to the tester via generics. | ||

[[File:sigmaDeltaTestbench.png|700px]] | [[File:sigmaDeltaTestbench.png|700px]] | ||

The modulator output is fed to a lowpass filter which reconstructs the original signal. | The modulator output is fed to a lowpass filter which reconstructs the original signal. | ||

| − | The lowpass | + | The lowpass we use also has a parameter <code>shiftBitNb</code> which can be used to shift the cutoff frequency octave by octave. |

| + | As a matter of fact, the testbench filter has the same structure as the sigma-delta modulator. | ||

| + | The only difference is that it hasn't a comparator at the output which reduces it to a single bit. | ||

[[Category:Components]] [[Category:Designs]] [[Category:VHDL]] [[Category:IP]] | [[Category:Components]] [[Category:Designs]] [[Category:VHDL]] [[Category:IP]] | ||

Revision as of 14:51, 14 June 2013

|

Sigma-Delta modulator

This IP can be found on the EDA Repository: svn: https://repos.hevs.ch/svn/eda/

The modulator architecture is of Cascaded Integrators with Distributed Feedback (CIDF).

Design

The coefficients can be chosen for the Signal Transfer Function (STF) to match any desired all-pole transfer function. This is done by writing the algebraic form of the modulator's STF and by comparing the denominator coefficients with the one of the desired transfer function. A Maxima script delivers the required coefficients.

An additional parameter, shiftBitNb is used to ensure stability.

Adding 1 to shiftBitNb reduces the STF by one octave (a factor of 2).

This value has to be adjusted within a simulation loop.

Entity

The VHDL entity of the modulator shows the generics, the inputs and the outputs:

ENTITY sigmaDeltaModulator IS

GENERIC(

signalBitNb : positive := 16;

shiftBitNb : natural := 1

);

PORT(

reset : IN std_ulogic;

clock : IN std_ulogic;

en : IN std_ulogic;

parallelIn : IN signed (signalBitNb-1 DOWNTO 0);

serialOut : OUT std_ulogic

);

The en would allow to work at a smaller frequency than the clock's.

As Sigma-Delta modulators should work at high rates, en is usually set to 1.

Testbench

The testbench generates a sinewave input to the modulator.

Clock and signal frequencies are defined as constants in the top-level architecture and passed to the tester via generics.

The modulator output is fed to a lowpass filter which reconstructs the original signal.

The lowpass we use also has a parameter shiftBitNb which can be used to shift the cutoff frequency octave by octave.

As a matter of fact, the testbench filter has the same structure as the sigma-delta modulator.

The only difference is that it hasn't a comparator at the output which reduces it to a single bit.