SEm/laboratoires/03 convertisseur

|

Convertisseur numérique / analogique

Introduction

Ce laboratoire permet de consolider les connaissances acquises sur le traitement de nombres. Il nous fournira un composant utile pour la suite: le convertisseur numérique / analogique. Il soulève certaines questions au sujet de la simulation de circuits de complexité moyenne. La conversion numérique / analogique se fera ici avec un modulateur sigma-delta (SD). Le signal original est codé en impulsions à une fréquence bien supérieure à la fréquence d'échantillonnage minimale. Le codage en impulsions est similaire à la modulation de largeur d'impulsions (Pulse Width Modulation, PWM) dans le fait que le signal d'origine se retrouve dans la moyenne des impulsions. A fréquences de fonctionnement identiques, le codage SD donne un meilleur rapport signal sur bruit que la PWM.

Modulateur de premier ordre

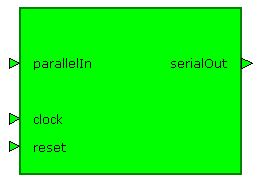

Le modulateur SD reçoit un signal numérique et le convertit en signal codé sur un bit, avec la forme d'un train d'impulsions.

Le modulateur SD de premier ordre peut se comprendre par l'analogie de la mesure du débit d'un cours d'eau:

- Le cours d'eau est amené dans un bassin qu'il va remplir.

- Dès que le niveau du bassin dépasse une ligne de référence, un opérateur retire un seau d'eau du bassin.

- Le débit moyen du cours d'eau est égal à la contenance du seau fois le nombre de seaux écopés par unité de temps.

Le modulateur se réalise comme suit:

- A chaque période d'horloge, la nouvelle valeur du signal est additionnée à un accumulateur.

- Le bit de poids fort du résultat est le signal de sortie du modulateur (impulsion ou pas).

- Si ce bit de poids fort est à '1', une valeur de 2n est soustraite à l'accumulateur, n étant le nombre de bits du signal à convertir.

Code VHDL

L'accumulateur interne a besoin de plus de bits que le signal d'entrée. Prévoir 4 bits supplémentaires et la simulation montrera le nombre effectivement nécessaire.

Simulation

L'amplitude du signal de sortie est donnée par la valeur moyenne de la sortie.

La restitution analogique du signal qui reste longtemps à '1' ou à '0' est délicate.

Modulateur de deuxième ordre

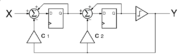

Le modulateur du deuxième ordre comporte deux accumulateurs. La figure suivante présente le modulateur à réaliser:

Pour ce circuit, les nombres seront considérés comme signés. Lorsque la valeur du second accumulateur est positive:

- La sortie vaut '1'.

- Une valeur de c1=2nBits-1 est retranchée du premier accumulateur.

- Une valeur de c2=2nBits+3 est retranchée du second accumulateur.

Lorsque la valeur du second accumulateur est négative:

- La sortie vaut '0'.

- Une valeur de c1=2nBits-1 est ajoutée au premier accumulateur.

- Une valeur de c2=2nBits+3 est ajoutée au second accumulateur.

La valeur nBits est le nombre de bits du signal d'entrée du modulateur, x.

Code VHDL

Prévoir pour chacun des accumulateurs 8 bits de plus que le signal d'entrée. Inverser le bit de poids fort du signal d'entrée et lui appliquer un gain de 7/8.

Simulation

Navigation

![]() 02 Générateur de fonctions avec calcul d'interpolation

02 Générateur de fonctions avec calcul d'interpolation

![]() Travaux de laboratoire

04 Synthèse automatique

Travaux de laboratoire

04 Synthèse automatique ![]()