HiRel/CanSat/Master FPGA

(→Connections) |

|||

| (41 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{TOC right}} | {{TOC right}} | ||

| − | This board will be the master board on the [[HiRel/CanSat]]. | + | This board will be the master board on the [[HiRel/CanSat|CanSat system]]. |

| + | |||

| + | {|class=wikitable | ||

| + | |- | ||

| + | ! Type || CanSat Master FPGA || Schematic || UCF || Description | ||

| + | |- | ||

| + | | V1.0 || [[File:CanSat_Master_FPGA_with_pin_numbers.jpg|450px|CanSat Master FPGA V1.0]] || [[Media:P-CAD EDA - CanSat Master FPGA schematic.pdf|CanSat Master FPGA Schematic PDF]] || [[Media:Cansat.ucf|CanSat Master FPGA UCF Files]] || Spartan 6 XC6SLX9 and 8Mb M25P80 SPI PROM | ||

| + | |- | ||

| + | |} | ||

= System = | = System = | ||

| − | The design contains a soft-core processor controlling the different slaves of the [[HiRel/CanSat]] | + | The design contains a soft-core processor controlling the different slaves of the [[HiRel/CanSat|CanSat]] |

via peripheral devices attached to it by an | via peripheral devices attached to it by an | ||

[http://en.wikipedia.org/wiki/Advanced_Microcontroller_Bus_Architecture#Advanced_High-performance_Bus_.28AHB.29 AHB-lite] bus system. | [http://en.wikipedia.org/wiki/Advanced_Microcontroller_Bus_Architecture#Advanced_High-performance_Bus_.28AHB.29 AHB-lite] bus system. | ||

== Connections == | == Connections == | ||

| + | |||

| + | The FPGA board hosts a 106.25 MHz oscillator and a button which can be used as a reset signal. | ||

| + | {|class=wikitable style="margin: 0 auto" | ||

| + | |- | ||

| + | ! Signal || FPGA pin || FPGA dir | ||

| + | |- | ||

| + | | clock || 16 || in | ||

| + | |- | ||

| + | | reset_n || 2 || in | ||

| + | |} | ||

The FPGA board connectors consist of 4 dual [http://en.wikipedia.org/wiki/Pmod_Interface Pmods], each having 12 pins. | The FPGA board connectors consist of 4 dual [http://en.wikipedia.org/wiki/Pmod_Interface Pmods], each having 12 pins. | ||

The Pmods are connected to the slave boards via the bottom and the top ring. | The Pmods are connected to the slave boards via the bottom and the top ring. | ||

| − | {|class=wikitable | + | {|class=wikitable style="margin: 0 auto" |

|- | |- | ||

| − | ! board || | + | ! board || connector || Signal || Pmod pin || FPGA pin || FPGA dir |

|- | |- | ||

| − | <!-- | + | <!-- slave A, XBee Board, bottom --> |

| − | | rowspan=4 | | + | | rowspan=8 | slave A:<br />[[HiRel/CanSat/Slave_XBee|Radio]] || rowspan=4 | bottom |

| + | | RxD || J1.2 || 126 || out | ||

| + | |- | ||

| + | | TxD || J1.4 || 123 || in | ||

| + | |- | ||

| + | | reset_n || J1.6 || 119 || out | ||

| + | |- | ||

| + | | sleep request || J1.8 || 117 || out | ||

|- | |- | ||

| − | | | + | <!-- slave A, Radio board, top --> |

| + | | rowspan=4 | top | ||

| + | | RSSI PWM || J3.1 || 134 || in | ||

| + | |- | ||

| + | | associate || J3.3 || 138 || in | ||

| + | |- | ||

| + | | DIO || J3.5 || 140 || inout | ||

| + | |- | ||

| + | | sleep_n || J3.7 || 142 || in | ||

|- | |- | ||

| − | | | + | <!-- slave B, Sensor board, bottom --> |

| + | | rowspan=8 | slave B:<br />[[HiRel/CanSat/Slave_Sensors|Sensors]] || rowspan=4 | bottom | ||

| + | | CS_n || J2.2 || 15 || out | ||

| + | |- | ||

| + | | MOSI || J2.4 || 12 || out | ||

| + | |- | ||

| + | | MISO || J2.6 || 9 || in | ||

| + | |- | ||

| + | | SClk || J2.8 || 6 || out | ||

|- | |- | ||

| − | | | + | <!-- slave B, sensor board, top --> |

| + | | rowspan=4 | top | ||

| + | | int_n || J4.1 || 24 || in | ||

| + | |- | ||

| + | | n.c. || J4.3 || 27 || | ||

| + | |- | ||

| + | | n.c. || J4.5 || 32 || | ||

| + | |- | ||

| + | | cnvt_n || J4.7 || 35 || out | ||

|- | |- | ||

| − | <!-- | + | <!-- slave C, power board, bottom --> |

| − | | rowspan=4 | | + | | rowspan=8 | slave C:<br />[[HiRel/CanSat/Slave_Power|Power]] || rowspan=4 | bottom |

| + | | TxD || J1.1 || 127 || in | ||

| + | |- | ||

| + | | RxD || J1.3 || 124 || out | ||

| + | |- | ||

| + | | LED 0 || J1.5 || 121 || out | ||

| + | |- | ||

| + | | LED 1 || J1.7 || 118 || out | ||

|- | |- | ||

| − | | | + | <!-- slave C, power board, top --> |

| − | |- | + | | rowspan=4 | top |

| − | | | + | | switch 4 || J3.2 || 133 || in |

| − | |- | + | |- |

| − | | | + | | switch 3 || J3.4 || 137 || in |

| + | |- | ||

| + | | switch 2 || J3.6 || 139 || in | ||

| + | |- | ||

| + | | switch 1 || J3.8 || 141|| in | ||

| + | |- | ||

| + | <!-- slave D, COM board, bottom --> | ||

| + | | rowspan=8 | slave D:<br />[[HiRel/CanSat/Slave_Gumstix|Computer On Module]] || rowspan=4 | bottom | ||

| + | | RxD1 || J2.1 || 14 || out | ||

| + | |- | ||

| + | | TxD1 || J2.3 || 11 || in | ||

| + | |- | ||

| + | | RESET_n || J2.5 || 8 || out | ||

| + | |- | ||

| + | | SPI CS1 || J2.7 || 5 || in | ||

|- | |- | ||

| + | <!-- slave D, COM board, top --> | ||

| + | | rowspan=4 | top | ||

| + | | SPI MISO || J4.2 || 23 || out | ||

| + | |- | ||

| + | | SPI MOSI || J4.4 || 26 || in | ||

| + | |- | ||

| + | | SPI CS0 || J4.6 || 30 || in | ||

| + | |- | ||

| + | | SPI CLK || J4.8 || 33 || un | ||

|} | |} | ||

| + | |||

| + | == Configuration Flash == | ||

| + | |||

| + | The FPGA has an attached M25P80 SPI flash of 8 Mb. | ||

= FPGA comparisons = | = FPGA comparisons = | ||

| Line 45: | Line 128: | ||

! Manufacturer || Device || Estimated Frequency || colspan="2" | LUTs / CoreCells || colspan="2" | Memory | ! Manufacturer || Device || Estimated Frequency || colspan="2" | LUTs / CoreCells || colspan="2" | Memory | ||

|- | |- | ||

| − | + | ! || || [MHz] || || % || Needed || Available | |

|- | |- | ||

| Xilinx || XC6SLX9 || 75.3 || 807 || 13 || 4 || 32 | | Xilinx || XC6SLX9 || 75.3 || 807 || 13 || 4 || 32 | ||

| Line 54: | Line 137: | ||

|} | |} | ||

| − | As it is visible in the table above, the smaller Microsemi Igloo devices are too small | + | As it is visible in the table above, the smaller Microsemi Igloo devices are too small. |

Bigger Microsemi Igloo devices however are not easily available and also quite expensive (>80$). | Bigger Microsemi Igloo devices however are not easily available and also quite expensive (>80$). | ||

On the other hand the Xilinx Spartan 6 FPGAs are quite spacious, immediately available and have a reasonable price (<20$). | On the other hand the Xilinx Spartan 6 FPGAs are quite spacious, immediately available and have a reasonable price (<20$). | ||

Furthermore we already use them successfully on our [http://wiki.hevs.ch/uit/index.php5/Hardware/FPGARack FPGArack] board. | Furthermore we already use them successfully on our [http://wiki.hevs.ch/uit/index.php5/Hardware/FPGARack FPGArack] board. | ||

| + | |||

| + | = BOM = | ||

| + | |||

| + | {|class=wikitable | ||

| + | |- | ||

| + | ! Device ||DigiKey Part No ||Description ||Quantity | ||

| + | |- | ||

| + | |XC6SLX9-2TQG144C ||122-1745-ND ||FPGA Xilinx Spartan 6 144TQF ||1 | ||

| + | |- | ||

| + | |FT232RL ||768-1007-1-ND ||FTDI IC USB FS SERIAL UART 28-SSOP ||1 | ||

| + | |- | ||

| + | |SC189CSKTRT ||SC189CSKCT-ND ||DC-DC 3.3->1.2 ||1 | ||

| + | |- | ||

| + | |10072354-G01-10ULF ||609-2961-ND ||FPGA programmer connector ||1 | ||

| + | |- | ||

| + | |CB3LV-3I-106M2500 ||CTX718LVCT-ND ||Oscillator 106.25MHz ||1 | ||

| + | |- | ||

| + | |CB2518T1R0M ||587-2184-1-ND ||INDUCTOR POWER 1.0uH 1007 ||1 | ||

| + | |- | ||

| + | |M25P80-VMN6TP ||M25P80-VMW6TGCT-ND ||SPI Flash ||1 | ||

| + | |- | ||

| + | |BLM18PG121SN1D ||490-1037-1-ND ||Ferrite Chip 120 Ohm ||1 | ||

| + | |- | ||

| + | |CC0805MKX5R5BB226 ||311-1464-1-ND ||CAP CER 22uF 6.3V 20% X5R 0805 ||1 | ||

| + | |- | ||

| + | |GRM21BR60J106ME19L|| ||CAP CER 10uF 6.3V 20% X5R 0805 ||1 | ||

| + | |- | ||

| + | |08056D475KAT2A ||478-1416-1-ND ||CAP 4.7uF 10% X5R 0805 ||14 | ||

| + | |- | ||

| + | |C1608X5R1A474K080AA ||445-1320-1-ND ||CAP 470nF 10% X5R 0603 ||10 | ||

| + | |- | ||

| + | ||| ||Resistance 0603 10k ||2 | ||

| + | |- | ||

| + | ||| ||Button ||2 | ||

| + | |} | ||

[[Category:Master]] [[Category:HiRel]] [[Category:CanSat]] | [[Category:Master]] [[Category:HiRel]] [[Category:CanSat]] | ||

Latest revision as of 17:22, 19 February 2018

|

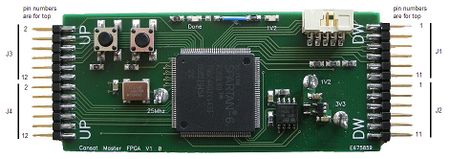

This board will be the master board on the CanSat system.

| Type | CanSat Master FPGA | Schematic | UCF | Description |

|---|---|---|---|---|

| V1.0 |  |

CanSat Master FPGA Schematic PDF | CanSat Master FPGA UCF Files | Spartan 6 XC6SLX9 and 8Mb M25P80 SPI PROM |

System

The design contains a soft-core processor controlling the different slaves of the CanSat via peripheral devices attached to it by an AHB-lite bus system.

Connections

The FPGA board hosts a 106.25 MHz oscillator and a button which can be used as a reset signal.

| Signal | FPGA pin | FPGA dir |

|---|---|---|

| clock | 16 | in |

| reset_n | 2 | in |

The FPGA board connectors consist of 4 dual Pmods, each having 12 pins. The Pmods are connected to the slave boards via the bottom and the top ring.

| board | connector | Signal | Pmod pin | FPGA pin | FPGA dir |

|---|---|---|---|---|---|

| slave A: Radio |

bottom | RxD | J1.2 | 126 | out |

| TxD | J1.4 | 123 | in | ||

| reset_n | J1.6 | 119 | out | ||

| sleep request | J1.8 | 117 | out | ||

| top | RSSI PWM | J3.1 | 134 | in | |

| associate | J3.3 | 138 | in | ||

| DIO | J3.5 | 140 | inout | ||

| sleep_n | J3.7 | 142 | in | ||

| slave B: Sensors |

bottom | CS_n | J2.2 | 15 | out |

| MOSI | J2.4 | 12 | out | ||

| MISO | J2.6 | 9 | in | ||

| SClk | J2.8 | 6 | out | ||

| top | int_n | J4.1 | 24 | in | |

| n.c. | J4.3 | 27 | |||

| n.c. | J4.5 | 32 | |||

| cnvt_n | J4.7 | 35 | out | ||

| slave C: Power |

bottom | TxD | J1.1 | 127 | in |

| RxD | J1.3 | 124 | out | ||

| LED 0 | J1.5 | 121 | out | ||

| LED 1 | J1.7 | 118 | out | ||

| top | switch 4 | J3.2 | 133 | in | |

| switch 3 | J3.4 | 137 | in | ||

| switch 2 | J3.6 | 139 | in | ||

| switch 1 | J3.8 | 141 | in | ||

| slave D: Computer On Module |

bottom | RxD1 | J2.1 | 14 | out |

| TxD1 | J2.3 | 11 | in | ||

| RESET_n | J2.5 | 8 | out | ||

| SPI CS1 | J2.7 | 5 | in | ||

| top | SPI MISO | J4.2 | 23 | out | |

| SPI MOSI | J4.4 | 26 | in | ||

| SPI CS0 | J4.6 | 30 | in | ||

| SPI CLK | J4.8 | 33 | un |

Configuration Flash

The FPGA has an attached M25P80 SPI flash of 8 Mb.

FPGA comparisons

The choice of the FPGA was based on a comparison of synthesis results of a simple AHB-Lite system.

| Manufacturer | Device | Estimated Frequency | LUTs / CoreCells | Memory | ||

|---|---|---|---|---|---|---|

| [MHz] | % | Needed | Available | |||

| Xilinx | XC6SLX9 | 75.3 | 807 | 13 | 4 | 32 |

| Microsemi | AGL60 | 16.4 | 56896 | 3704 | 2 | 4 |

| Microsemi | AGL250 | |||||

As it is visible in the table above, the smaller Microsemi Igloo devices are too small. Bigger Microsemi Igloo devices however are not easily available and also quite expensive (>80$). On the other hand the Xilinx Spartan 6 FPGAs are quite spacious, immediately available and have a reasonable price (<20$). Furthermore we already use them successfully on our FPGArack board.

BOM

| Device | DigiKey Part No | Description | Quantity |

|---|---|---|---|

| XC6SLX9-2TQG144C | 122-1745-ND | FPGA Xilinx Spartan 6 144TQF | 1 |

| FT232RL | 768-1007-1-ND | FTDI IC USB FS SERIAL UART 28-SSOP | 1 |

| SC189CSKTRT | SC189CSKCT-ND | DC-DC 3.3->1.2 | 1 |

| 10072354-G01-10ULF | 609-2961-ND | FPGA programmer connector | 1 |

| CB3LV-3I-106M2500 | CTX718LVCT-ND | Oscillator 106.25MHz | 1 |

| CB2518T1R0M | 587-2184-1-ND | INDUCTOR POWER 1.0uH 1007 | 1 |

| M25P80-VMN6TP | M25P80-VMW6TGCT-ND | SPI Flash | 1 |

| BLM18PG121SN1D | 490-1037-1-ND | Ferrite Chip 120 Ohm | 1 |

| CC0805MKX5R5BB226 | 311-1464-1-ND | CAP CER 22uF 6.3V 20% X5R 0805 | 1 |

| GRM21BR60J106ME19L | CAP CER 10uF 6.3V 20% X5R 0805 | 1 | |

| 08056D475KAT2A | 478-1416-1-ND | CAP 4.7uF 10% X5R 0805 | 14 |

| C1608X5R1A474K080AA | 445-1320-1-ND | CAP 470nF 10% X5R 0603 | 10 |

| Resistance 0603 10k | 2 | ||

| Button | 2 |