Standards/HEI 'VME' Backplane Bus

|

Based on the VMEbus and inspired by the ARM AMBA3 AHB-Lite, this backplane bus is synchronous and master-slave oriented.

Bus Specifications

The table below presents its signals, which can be divided into three groups:

- The main parallel bus

- Some serial buses (UART, SPI, I2C)

- The power supply

The main parallel bus is like a CPU bus, with address and data. All operations are synchronous relatively to the main clock MCLK. The master can write or read on slaves, via the usage of the signals Axx (address), Dxx (data), WR (write/read operation flag), and EN (enable operation). Please note that the data bus is bidirectional.

For applications with less data bandwidth but higher data integrity specifications, a Hamming error correction code can be used for manage small errors (2-bit error detection, 1-bit error correction). The extra signals managing the ECC functionality (bidirectional) and the MFREEZE / SREADY flags (asynchronous).

| Signal | Width | Driver | Description | |

|---|---|---|---|---|

| Axx | 8/16 bit | Master | Address bus | |

| Dxx | 16/32 bit | Master/Slave | Data bus | |

| ECCxx | 6/8 bit | Master/Slave | ECC bits (7 Hamming Bits + 1 Parity Bit) | |

| MCLK | 1 bit | Master | Main bus clock | |

| RST | 1 bit | Master | ReSeT. Allow the master to reset all slaves racks. | |

| EN | 1 bit | Master | Enables bus transaction. | |

| WR | 1 bit | Master | WRite operation when set, else read operation. | |

| SREADY | 1 bit | Slave | Slave READY. Pulled low by slave when not ready or when ECC error occurs. | |

| MFREEZE | 1 bit | Master | Master FREEZE. Set by the master for freeze the bus when ECC error occurs. | |

| MODE | 1 bit | Master | '1' is 64k*32bit slave card and '0' 256*16bit slave card. Used as MSB bit of address. | |

| WCLKx | 2 bit | Undef. | Additionnal clock lines. | |

| IRQxx | 8 bit | Undef. | User-defined interrupt bits. | |

| UART_TXD | 1 bit | Master | UART-Bus transmission line | |

| UART_RXD | 1 bit | Slave | UART-Bus receiving line | |

| SPI_CLK | 1 bit | Master | SPI-Bus clock signal | |

| SPI_MISO | 1 bit | Slave | SPI-Bus Master In Slave Out | |

| SPI_MOSI | 1 bit | Master | SPI-Bus Master Out Slave In | |

| SPI_CS0 | 1 bit | Master | SPI-Bus Chip-Select 0 | |

| SPI_CS1 | 1 bit | Master | SPI-Bus Chip-Select 1 | |

| I2C_SCL | 1 bit | Master | I2C-Bus clock line | |

| I2C_SDA | 1 bit | Bi-Directionel | I2C-Bus data line | |

| +12V | - | Backplane | +12V as defined by the VME Standart | |

| -12V | - | Backplane | -12V as defined by the VME Standart | |

| USER_VDD | - | Backplane | Free definable user voltage | |

| +5V_F | - | Backplane | Filtered +5V for all "Clean" consumers | |

| +5V_N | - | Backplane | +5V for all "Noisy" consumers | |

| +3.3V | - | Backplane | Filtered +3.3V voltage for all "clean" consumers | |

| GND_N | - | Backplane | Gnd for all "Noisy" Voltages. That means -12V / +12V / User_VDD / +5V_N | |

| GND_F | - | Backplane | Ground for all "Clean" Voltages e.g. +5V_F / +3.3V |

Signal Mapping

The bus can be shared by boards with full bus width (HVME32) and halved bus width (HVME16). If the master is HVME32, slaves HVME32 and HVME16 can co-exist, with or without ECC individually. However, if the master is HVME16, all slaves cards must be implicitly HVME16.

3 Row - 96Pin functionality (HVME32)

10 IRQ bits are available and freely usable for the target application. However, some pins have shared functions. E.g. ECC and IRQ uses the same pin. Therefore its functionality need to be choosen during development, and can minimize the number of IRQ Pins available.

The table below represents the signal mapping on the DIN41612 3x32pin.

Some well-known serial protocols (UART, SPI, I2C) have been added to the mapping for allow simple communications with and between cards which are only equipped with µC because of their incapacity to interface the main parallel bus.

For the power supply, grounds and voltages have been placed to grant compatibility with VME backplanes. A +3.3V pin has been added and a distinction between clean (*_F) voltages for voltage sensitive operations like ADC, DAC and noisy (*_N) voltages for voltage insensitive usage has been added, this functionality can be bypassed if necessary.

2 Row - 64Pin functionality (HVME16)

For physical reasons (notably routing 2 layer “HES-SO” PCB with small FPGA/µC), there is the possibility to use the A and C row only – therefore, the data (Dxx) and the address (Axx) bus are both divided by two. The bus can host both 3 rows (A15..0/D31..0) and 2 rows (A7..0/D15..0) slave boards, respectively named 32bit and 16bit slaves. Addressing of each type of slave is done with the MODE bit, acting like an “Axx’high+1” address bit. Note that ECC is supported for both modes (16bit mode use less ECCxx bits – 5 instead of 7). The last ECC bit (ECC07 or ECC05) is de facto not used, but reserved for further better ECC coding.

| Row A | Row B | Row C | |

|---|---|---|---|

| 01 | D00 | A08 | D08 |

| 02 | D01 | A09 | D09 |

| 03 | D02 | A10 | D10 |

| 04 | D03 | A11 | D11 |

| 05 | D04 | A12 | D12 |

| 06 | D05 | A13 | D13 |

| 07 | D06 | A14 | D14 |

| 08 | D07 | A15 | D15 |

| 09 | GND_N | D16 | GND_N |

| 10 | MCLK1 | D17 | RST |

| 11 | GND_N | D18 | WR |

| 12 | MFREEZE1 | D19 | EN |

| 13 | SREADY1 | D20 | UART_RXD |

| 14 | MODE | D21 | UART_TXD |

| 15 | GND_N | D22 | SPI_CS1 |

| 16 | WCLK0 | D231 | IRQ10 / ECC00 |

| 17 | GND_N | D241 | IRQ9 / ECC01 |

| 18 | SPI_CLK | GND_F | IRQ8 / ECC021 |

| 19 | GND_N | WCLK1 | GND_F1 |

| 20 | SPI_MISO | GND_N | I2C_SCL |

| 21 | SPI_MOSI | ECC061 | IRQ7 / ECC03 |

| 22 | SPI_CS0 | ECC07 | I2C_SDA |

| 23 | A07 | GND_N | IRQ6 / ECC04 |

| 24 | A06 | D25 | IRQ5 / ECC05 |

| 25 | A05 | D26 | IRQ4 |

| 26 | A04 | D27 | IRQ3 |

| 27 | A03 | D28 | IRQ2 |

| 28 | A02 | D29 | IRQ1 |

| 29 | A01 | D30 | IRQ0 |

| 30 | A00 | D31 | +3.3V_F |

| 31 | -12V | USER_VDD | +12V |

| 32 | +5V_N | +5V_N | +5V_F |

1 These pins connect to a GCLK pin on the FPGA

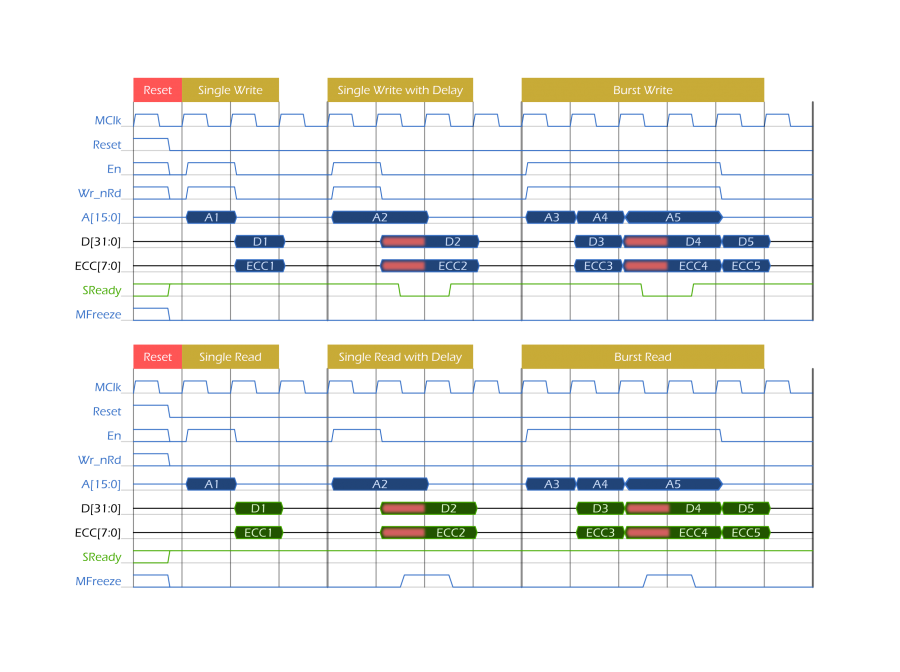

Timing diagrams

The upper graph presents a write operation, where the master set the address (with corresponding ECC code) and the EN / WR flags. Next cycle, the data are placed on bus. The slave can pull-down the SReady line until the ECC code verifies correct data integrity on the bus.

The lower graph shows a read operation in which the master set the address and the EN / WR flags. Next cycle, the slave takes control of the data line and places the corresponding data. In case of integrity failure, the master set high the MFreeze until data is considered as valid by verifying the ECC.

All operation can be pipelined, including interleaved read/writes.

The slave could hold down the SReady line until the read/write operation is done, but this case has not been considered yet.

- NB #1 The used Hamming ECC code can only detect errors on 2 bits and correct only errors on 1 bit. In case of wider data corruption (> 2 bits), corrupted data can be interpreted as valid by the master as well as the slave controller.

- NB #2 When ECC is active, a big asynchronous loop is present between Dxx/ECCxx and SReady/MFreeze lines (Master

Slave for write operations and Slave

Slave for write operations and Slave Master for read operation). This reduces considerably the max bus speed. Furthermore it has a great negative impact on the line quality and distance between master/slaves.

Master for read operation). This reduces considerably the max bus speed. Furthermore it has a great negative impact on the line quality and distance between master/slaves.