Hardware/FPGARackEdison

(Difference between revisions)

(→On-board USB communication) |

(→VME connection) |

||

| Line 38: | Line 38: | ||

making it compatible with the other [[Hardware#FPGA_Rack|HEI VME rack]] components. | making it compatible with the other [[Hardware#FPGA_Rack|HEI VME rack]] components. | ||

The Edison cluster board can thus be used for controlling an instrument built out of these devices. | The Edison cluster board can thus be used for controlling an instrument built out of these devices. | ||

| + | |||

| + | Connected signals are: | ||

| + | * parallel bus: A7 ÷ A0, D15 ÷ D0, en, wr, ready, freeze, mode | ||

| + | * SPI bus | ||

= On-board logic levels = | = On-board logic levels = | ||

Revision as of 13:03, 24 November 2015

|

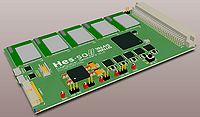

Board Overview

| Type | FPGA Rack | Schematic | User constraints file | Description |

|---|---|---|---|---|

| V1.0 | FPGA Rack Edison v1.0 | FPGA-Rack Edison v1.0 Schematic PDF | TBD | 5 Intel Edison Compute Modules and Microsemi AGL1000 FPGA |

The board is compatible with the FPGA Rack Backplane for interconnecting different boards with the help of the HES-SO Backplane Bus and the HES-SO VME IP Core. Some restrictions due to IOs availablity are shown in the following chapter.

Hardware features

The board comprises a controller FPGA and Linux microprocessor systems. It is tailored for low-power, real-time image processing.

Intel Edison compute modules

The board can host up to 5 Intel Edison compute modules.

On-board communication

The FPGA connects to each compute module individually with:

- a serial port

- a SPI link

- an USB FIFO circuit

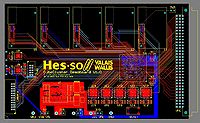

VME connection

The VME connector at the back is compatible with the HEI Backplane Bus, making it compatible with the other HEI VME rack components. The Edison cluster board can thus be used for controlling an instrument built out of these devices.

Connected signals are:

- parallel bus: A7 ÷ A0, D15 ÷ D0, en, wr, ready, freeze, mode

- SPI bus

On-board logic levels

TBD

Programmation

TBD