|

|

| (18 intermediate revisions by 2 users not shown) |

| Line 6: |

Line 6: |

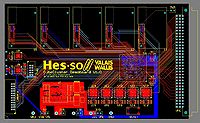

| | [[File:FPGARackEdison_pcb_v1_0.jpg|200px|FPGA Rack Edison V1.0 PCB layout]] | | [[File:FPGARackEdison_pcb_v1_0.jpg|200px|FPGA Rack Edison V1.0 PCB layout]] |

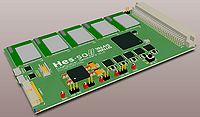

| | [[File:FPGARackEdison photo v1 0.jpg|200px|FPGA Rack Edison V1.0 photo]] | | [[File:FPGARackEdison photo v1 0.jpg|200px|FPGA Rack Edison V1.0 photo]] |

| | + | [[File:Cubeclusterdemoboard_v1.jpg|200px|FPGA Rack Edison V1.0 fully mounted]] |

| | | | |

| | {|class=wikitable | | {|class=wikitable |

| Line 15: |

Line 16: |

| | |} | | |} |

| | | | |

| − | The board is compatible with the [[Hardware/FPGARackBackplane|FPGA Rack Backplane]] for interconnecting different boards with the help of the [[Standards/HEVs_'VME'_Backplane_Bus|HES-SO Backplane Bus]] and the [[Components/IP/VME|HES-SO VME IP Core]]. Some restrictions due to IOs availablity are shown in the following chapter. | + | The board comprises a controller FPGA and Linux microprocessor systems. |

| | + | It is tailored for low-power, real-time image processing. |

| | + | The board is compatible with the [[Hardware/FPGARackBackplane|FPGA Rack Backplane]] for interconnecting different boards. |

| | | | |

| − | = HEVS VME Compatibility =

| + | A [http://www.hevs.ch/en/rad-instituts/institute-of-systems-engineering/projects/low-power-high-performance-unit-for-cubesat-10440 short presentation] |

| | + | is given on the Institute's website. |

| | | | |

| − | {| class="wikitable" style="margin: 0 auto; text-align: center;"

| + | = Hardware features = |

| − | |- style="text-align:left;"

| + | |

| − | ! style="width:8px"|

| + | == Power supplies == |

| − | ! style="width:64px"|Signal

| + | |

| − | ! style="width:64px"|Width

| + | The FPGA while programming and running must hold the following bank voltages : |

| − | ! style="width:64px"|Driver

| + | * Bank 0 : 3.3V |

| − | ! style="width:512px ; text-align:left"|Description

| + | * Bank 1 : 3.3V |

| − | |-

| + | * Bank 2 : 1.8V (Big Fat Warning! This bank is used to communicate with the Edisons I/Os which operate at 1.8V.) |

| − | ! style="background:#c6efce" |

| + | * Bank 3 : 3.3V |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''Axx'''</span>

| + | |

| − | | style="background:#ffffff" | 8/16 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | Address bus

| + | |

| − | |-

| + | |

| − | ! style="background:#7ac1ff" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''Dxx'''</span>

| + | |

| − | | style="background:#ffffff" | 16/32 bit

| + | |

| − | | style="background:#ffffff" | Master/Slave

| + | |

| − | | style="background:#ffffff ; text-align:left" | Data bus

| + | |

| − | |-

| + | |

| − | ! style="background:#ffcc77" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''ECCxx'''</span>

| + | |

| − | | style="background:#ffffff" | 6/8 bit

| + | |

| − | | style="background:#ffffff" | Master/Slave

| + | |

| − | | style="background:#ffffff ; text-align:left" | ECC bits (7 Hamming Bits + 1 Parity Bit)

| + | |

| − | |-

| + | |

| − | ! style="background:#ff3a3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''MCLK'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | Main bus clock

| + | |

| − | |-

| + | |

| − | ! style="background:#ff3a3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''RST'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | ReSeT. Allow the master to reset all slaves racks.

| + | |

| − | |-

| + | |

| − | ! style="background:#ffaaff" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''EN'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | Enables bus transaction.

| + | |

| − | |-

| + | |

| − | ! style="background:#ffaaff" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''WR'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | WRite operation when set, else read operation.

| + | |

| − | |-

| + | |

| − | ! style="background:#ffaaff" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''SREADY'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Slave

| + | |

| − | | style="background:#ffffff ; text-align:left" | Slave READY. Pulled low by slave when not ready or when ECC error occurs.

| + | |

| − | |-

| + | |

| − | ! style="background:#ffaaff" | | + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''MFREEZE'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | Master FREEZE. Set by the master for freeze the bus when ECC error occurs.

| + | |

| − | |-

| + | |

| − | ! style="background:#ffaaff" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''MODE'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | '1' is 64k*32bit slave card and '0' 256*16bit slave card. Used as MSB bit of address.

| + | |

| − | |-

| + | |

| − | ! style="background:#7fff7a" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''WCLKx'''</span>

| + | |

| − | | style="background:#ffffff" | 2 bit

| + | |

| − | | style="background:#ffffff" | Undef.

| + | |

| − | | style="background:#ffffff ; text-align:left" | Additionnal clock lines.

| + | |

| − | |-

| + | |

| − | ! style="background:#ffee77" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''IRQxx'''</span>

| + | |

| − | | style="background:#ffffff" | 8 bit

| + | |

| − | | style="background:#ffffff" | Undef.

| + | |

| − | | style="background:#ffffff ; text-align:left" | User-defined interrupt bits.

| + | |

| − | |-

| + | |

| − | ! style="background:#DA9694" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''UART_TXD'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | UART-Bus transmission line

| + | |

| − | |-

| + | |

| − | ! style="background:#DA9694" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''UART_RXD'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Slave

| + | |

| − | | style="background:#ffffff ; text-align:left" | UART-Bus receiving line

| + | |

| − | |-

| + | |

| − | ! style="background:#b1a0c7" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''SPI_CLK'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | SPI-Bus clock signal

| + | |

| − | |-

| + | |

| − | ! style="background:#b1a0c7" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''SPI_MISO'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Slave

| + | |

| − | | style="background:#ffffff ; text-align:left" | SPI-Bus Master In Slave Out

| + | |

| − | |-

| + | |

| − | ! style="background:#b1a0c7" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''SPI_MOSI'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | SPI-Bus Master Out Slave In

| + | |

| − | |-

| + | |

| − | ! style="background:#b1a0c7" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''SPI_CS0'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | SPI-Bus Chip-Select 0

| + | |

| − | |-

| + | |

| − | ! style="background:#b1a0c7" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''SPI_CS1'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | SPI-Bus Chip-Select 1

| + | |

| − | |-

| + | |

| − | ! style="background:#c4bd97" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''I2C_SCL'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Master

| + | |

| − | | style="background:#ffffff ; text-align:left" | I2C-Bus clock line

| + | |

| − | |-

| + | |

| − | ! style="background:#c4bd97" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''I2C_SDA'''</span>

| + | |

| − | | style="background:#ffffff" | 1 bit

| + | |

| − | | style="background:#ffffff" | Bi-Directionel

| + | |

| − | | style="background:#ffffff ; text-align:left" | I2C-Bus data line

| + | |

| − | |-

| + | |

| − | ! style="background:#3f3f3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''+12V'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | +12V as defined by the VME Standart

| + | |

| − | |-

| + | |

| − | ! style="background:#3f3f3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''-12V'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | -12V as defined by the VME Standart

| + | |

| − | |-

| + | |

| − | ! style="background:#3f3f3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''USER_VDD'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | Free definable user voltage

| + | |

| − | |-

| + | |

| − | ! style="background:#3f3f3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''+5V_F'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | Filtered +5V for all "Clean" consumers

| + | |

| − | |-

| + | |

| − | ! style="background:#3f3f3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''+5V_N'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | +5V for all "Noisy" consumers

| + | |

| − | |-

| + | |

| − | ! style="background:#3f3f3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''+3.3V'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | Filtered +3.3V voltage for all "clean" consumers

| + | |

| − | |-

| + | |

| − | ! style="background:#3f3f3f" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''GND_N'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | Gnd for all "Noisy" Voltages. That means -12V / +12V / User_VDD / +5V_N

| + | |

| − | |-

| + | |

| − | ! style="background:#cccccc" |

| + | |

| − | | style="background:#3f3f3f" | <span style="color:#FFFFFF">'''GND_F'''</span>

| + | |

| − | | style="background:#ffffff" | -

| + | |

| − | | style="background:#ffffff" | Backplane

| + | |

| − | | style="background:#ffffff ; text-align:left" | Ground for all "Clean" Voltages e.g. +5V_F / +3.3V

| + | |

| − | |}

| + | |

| | | | |

| − | = Hardware features =

| |

| − | TBD

| |

| | == Intel Edison compute modules == | | == Intel Edison compute modules == |

| − | TBD

| |

| − | == On-board USB communication ==

| |

| − | TBD

| |

| | | | |

| − | = On-board logic levels = | + | The board can host up to 5 [http://ark.intel.com/products/84572/Intel-Edison-Compute-Module-IoT Intel Edison compute modules]. |

| − | TBD

| + | |

| | + | == On-board communication == |

| | + | |

| | + | The FPGA connects to each compute module individually with: |

| | + | * a serial port |

| | + | * a SPI link, tested up to 6 Mbit/s |

| | + | * an [http://www.ftdichip.com/Products/ICs/FT232H.htm USB FIFO] circuit, tested up to 400 Mbit/s |

| | + | |

| | + | Additionally, the FPGA connects to a general purpose 24-pin connector and to a VME backplane connector. |

| | + | The 24-pin connector is foreseen for interfacing a camera. |

| | + | |

| | + | == VME connection == |

| | + | |

| | + | The VME connector at the back is compatible with the [[Standards/HEI_%27VME%27_Backplane_Bus|HEI Backplane Bus]], |

| | + | making it compatible with the other [[Hardware#FPGA_Rack|HEI VME rack]] components. |

| | + | The Edison cluster board can thus be used for controlling an instrument built out of these devices. |

| | + | |

| | + | Connected signals are: |

| | + | * backplane controls: MCLK, RST, WCLK0, WCLK1 |

| | + | * parallel bus: A7 ÷ A0, D15 ÷ D0, en, wr, ready, freeze, mode |

| | + | * SPI bus: CLK, MISO, MOSI, CS0, CS1 |

| | + | * I2C bus: SCl, SDa |

| | + | * UART: RxD, TxD |

| | | | |

| | = Programmation = | | = Programmation = |

| − | TBD

| + | By default, the PWR header can be leaved open. This header is used as a debug power header for the Edison in slot U1 (which one with the USB console output called Debug). The FPGA present on the board contains by default a minimal circuit which already drives the power pin of the Edison and the FTDI USB-FIFO circuit. |

| | + | |

| | + | == Design & Programmer Tools == |

| | + | |

| | + | You can use the [[Hardware/Programmers|Actel FlashPro4]] with the Libero Suite to design your FPGA circuit and program the FPGA. |

| | | | |

| | = Datasheets = | | = Datasheets = |

The board comprises a controller FPGA and Linux microprocessor systems.

It is tailored for low-power, real-time image processing.

The board is compatible with the FPGA Rack Backplane for interconnecting different boards.

Additionally, the FPGA connects to a general purpose 24-pin connector and to a VME backplane connector.

The 24-pin connector is foreseen for interfacing a camera.

By default, the PWR header can be leaved open. This header is used as a debug power header for the Edison in slot U1 (which one with the USB console output called Debug). The FPGA present on the board contains by default a minimal circuit which already drives the power pin of the Edison and the FTDI USB-FIFO circuit.