Hardware/FPGARackEdison

(→VME connection) |

|||

| (12 intermediate revisions by 2 users not shown) | |||

| Line 6: | Line 6: | ||

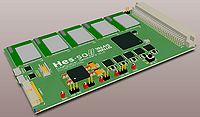

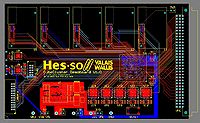

[[File:FPGARackEdison_pcb_v1_0.jpg|200px|FPGA Rack Edison V1.0 PCB layout]] | [[File:FPGARackEdison_pcb_v1_0.jpg|200px|FPGA Rack Edison V1.0 PCB layout]] | ||

[[File:FPGARackEdison photo v1 0.jpg|200px|FPGA Rack Edison V1.0 photo]] | [[File:FPGARackEdison photo v1 0.jpg|200px|FPGA Rack Edison V1.0 photo]] | ||

| + | [[File:Cubeclusterdemoboard_v1.jpg|200px|FPGA Rack Edison V1.0 fully mounted]] | ||

{|class=wikitable | {|class=wikitable | ||

| Line 15: | Line 16: | ||

|} | |} | ||

| − | The board is compatible with the [[Hardware/FPGARackBackplane|FPGA Rack Backplane]] for interconnecting different boards | + | The board comprises a controller FPGA and Linux microprocessor systems. |

| + | It is tailored for low-power, real-time image processing. | ||

| + | The board is compatible with the [[Hardware/FPGARackBackplane|FPGA Rack Backplane]] for interconnecting different boards. | ||

| + | |||

| + | A [http://www.hevs.ch/en/rad-instituts/institute-of-systems-engineering/projects/low-power-high-performance-unit-for-cubesat-10440 short presentation] | ||

| + | is given on the Institute's website. | ||

= Hardware features = | = Hardware features = | ||

| − | The | + | == Power supplies == |

| − | + | ||

| + | The FPGA while programming and running must hold the following bank voltages : | ||

| + | * Bank 0 : 3.3V | ||

| + | * Bank 1 : 3.3V | ||

| + | * Bank 2 : 1.8V (Big Fat Warning! This bank is used to communicate with the Edisons I/Os which operate at 1.8V.) | ||

| + | * Bank 3 : 3.3V | ||

== Intel Edison compute modules == | == Intel Edison compute modules == | ||

| Line 30: | Line 41: | ||

The FPGA connects to each compute module individually with: | The FPGA connects to each compute module individually with: | ||

* a serial port | * a serial port | ||

| − | * a SPI link | + | * a SPI link, tested up to 6 Mbit/s |

| − | * an [http://www.ftdichip.com/Products/ICs/FT232H.htm USB FIFO] circuit | + | * an [http://www.ftdichip.com/Products/ICs/FT232H.htm USB FIFO] circuit, tested up to 400 Mbit/s |

| + | |||

| + | Additionally, the FPGA connects to a general purpose 24-pin connector and to a VME backplane connector. | ||

| + | The 24-pin connector is foreseen for interfacing a camera. | ||

== VME connection == | == VME connection == | ||

| − | The VME connector at the back is compatible with the [[Standards/ | + | The VME connector at the back is compatible with the [[Standards/HEI_%27VME%27_Backplane_Bus|HEI Backplane Bus]], |

making it compatible with the other [[Hardware#FPGA_Rack|HEI VME rack]] components. | making it compatible with the other [[Hardware#FPGA_Rack|HEI VME rack]] components. | ||

The Edison cluster board can thus be used for controlling an instrument built out of these devices. | The Edison cluster board can thus be used for controlling an instrument built out of these devices. | ||

Connected signals are: | Connected signals are: | ||

| + | * backplane controls: MCLK, RST, WCLK0, WCLK1 | ||

* parallel bus: A7 ÷ A0, D15 ÷ D0, en, wr, ready, freeze, mode | * parallel bus: A7 ÷ A0, D15 ÷ D0, en, wr, ready, freeze, mode | ||

| − | * SPI bus | + | * SPI bus: CLK, MISO, MOSI, CS0, CS1 |

| − | + | * I2C bus: SCl, SDa | |

| − | + | * UART: RxD, TxD | |

| − | + | ||

= Programmation = | = Programmation = | ||

| − | + | By default, the PWR header can be leaved open. This header is used as a debug power header for the Edison in slot U1 (which one with the USB console output called Debug). The FPGA present on the board contains by default a minimal circuit which already drives the power pin of the Edison and the FTDI USB-FIFO circuit. | |

| + | |||

| + | == Design & Programmer Tools == | ||

| + | |||

| + | You can use the [[Hardware/Programmers|Actel FlashPro4]] with the Libero Suite to design your FPGA circuit and program the FPGA. | ||

= Datasheets = | = Datasheets = | ||

Latest revision as of 12:44, 12 December 2016

|

Board Overview

| Type | FPGA Rack | Schematic | User constraints file | Description |

|---|---|---|---|---|

| V1.0 | FPGA Rack Edison v1.0 | FPGA-Rack Edison v1.0 Schematic PDF | TBD | 5 Intel Edison Compute Modules and Microsemi AGL1000 FPGA |

The board comprises a controller FPGA and Linux microprocessor systems. It is tailored for low-power, real-time image processing. The board is compatible with the FPGA Rack Backplane for interconnecting different boards.

A short presentation is given on the Institute's website.

Hardware features

Power supplies

The FPGA while programming and running must hold the following bank voltages :

- Bank 0 : 3.3V

- Bank 1 : 3.3V

- Bank 2 : 1.8V (Big Fat Warning! This bank is used to communicate with the Edisons I/Os which operate at 1.8V.)

- Bank 3 : 3.3V

Intel Edison compute modules

The board can host up to 5 Intel Edison compute modules.

On-board communication

The FPGA connects to each compute module individually with:

- a serial port

- a SPI link, tested up to 6 Mbit/s

- an USB FIFO circuit, tested up to 400 Mbit/s

Additionally, the FPGA connects to a general purpose 24-pin connector and to a VME backplane connector. The 24-pin connector is foreseen for interfacing a camera.

VME connection

The VME connector at the back is compatible with the HEI Backplane Bus, making it compatible with the other HEI VME rack components. The Edison cluster board can thus be used for controlling an instrument built out of these devices.

Connected signals are:

- backplane controls: MCLK, RST, WCLK0, WCLK1

- parallel bus: A7 ÷ A0, D15 ÷ D0, en, wr, ready, freeze, mode

- SPI bus: CLK, MISO, MOSI, CS0, CS1

- I2C bus: SCl, SDa

- UART: RxD, TxD

Programmation

By default, the PWR header can be leaved open. This header is used as a debug power header for the Edison in slot U1 (which one with the USB console output called Debug). The FPGA present on the board contains by default a minimal circuit which already drives the power pin of the Edison and the FTDI USB-FIFO circuit.

Design & Programmer Tools

You can use the Actel FlashPro4 with the Libero Suite to design your FPGA circuit and program the FPGA.