Hardware/FPGARackEdison

From UIT

Revision as of 11:58, 17 November 2015 by Francois.corthay (Talk | contribs)

|

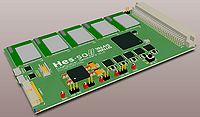

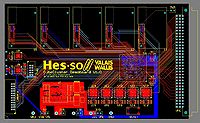

Board Overview

| Type | FPGA Rack | Schematic | User constraints file | Description |

|---|---|---|---|---|

| V1.0 | FPGA Rack Edison v1.0 | FPGA-Rack Edison v1.0 Schematic PDF | TBD | 5 Intel Edison Compute Modules and Microsemi AGL1000 FPGA |

The board is compatible with the FPGA Rack Backplane for interconnecting different boards with the help of the HES-SO Backplane Bus and the HES-SO VME IP Core. Some restrictions due to IOs availablity are shown in the following chapter.

HEVS VME Compatibility

| Signal | Width | Driver | Description | |

|---|---|---|---|---|

| Axx | 8/16 bit | Master | Address bus | |

| Dxx | 16/32 bit | Master/Slave | Data bus | |

| ECCxx | 6/8 bit | Master/Slave | ECC bits (7 Hamming Bits + 1 Parity Bit) | |

| MCLK | 1 bit | Master | Main bus clock | |

| RST | 1 bit | Master | ReSeT. Allow the master to reset all slaves racks. | |

| EN | 1 bit | Master | Enables bus transaction. | |

| WR | 1 bit | Master | WRite operation when set, else read operation. | |

| SREADY | 1 bit | Slave | Slave READY. Pulled low by slave when not ready or when ECC error occurs. | |

| MFREEZE | 1 bit | Master | Master FREEZE. Set by the master for freeze the bus when ECC error occurs. | |

| MODE | 1 bit | Master | '1' is 64k*32bit slave card and '0' 256*16bit slave card. Used as MSB bit of address. | |

| WCLKx | 2 bit | Undef. | Additionnal clock lines. | |

| IRQxx | 8 bit | Undef. | User-defined interrupt bits. | |

| UART_TXD | 1 bit | Master | UART-Bus transmission line | |

| UART_RXD | 1 bit | Slave | UART-Bus receiving line | |

| SPI_CLK | 1 bit | Master | SPI-Bus clock signal | |

| SPI_MISO | 1 bit | Slave | SPI-Bus Master In Slave Out | |

| SPI_MOSI | 1 bit | Master | SPI-Bus Master Out Slave In | |

| SPI_CS0 | 1 bit | Master | SPI-Bus Chip-Select 0 | |

| SPI_CS1 | 1 bit | Master | SPI-Bus Chip-Select 1 | |

| I2C_SCL | 1 bit | Master | I2C-Bus clock line | |

| I2C_SDA | 1 bit | Bi-Directionel | I2C-Bus data line | |

| +12V | - | Backplane | +12V as defined by the VME Standart | |

| -12V | - | Backplane | -12V as defined by the VME Standart | |

| USER_VDD | - | Backplane | Free definable user voltage | |

| +5V_F | - | Backplane | Filtered +5V for all "Clean" consumers | |

| +5V_N | - | Backplane | +5V for all "Noisy" consumers | |

| +3.3V | - | Backplane | Filtered +3.3V voltage for all "clean" consumers | |

| GND_N | - | Backplane | Gnd for all "Noisy" Voltages. That means -12V / +12V / User_VDD / +5V_N | |

| GND_F | - | Backplane | Ground for all "Clean" Voltages e.g. +5V_F / +3.3V |

Hardware features

TBD

Intel Edison compute modules

TBD

On-board USB communication

TBD

On-board logic levels

TBD

Programmation

TBD