Hardware/FPGARackHiRADDAV1

m |

m (→Showroom) |

||

| (12 intermediate revisions by 2 users not shown) | |||

| Line 7: | Line 7: | ||

! Type || FPGA Rack || Documentation || Description | ! Type || FPGA Rack || Documentation || Description | ||

|- | |- | ||

| − | | V1.00 || [[File: | + | | V1.00 || [[File:HIRADDA_POWER_WITHCORE.jpg|256px|HiRADDA Core V1.00 (with power)]] || <center> [[File:ICO_LOCKCLOSE_24PX.png|Restricted access]] <br> [[Hardware/PrivateResources|Full documentation]] || '''Kintex7 XC7K160T-xFFG676''' <br> 2x ADS1675 <br> 1x MAX5888 <br> 1x AD9517-4 <br> DDR3, NOR Flash, F/MRAM <br> Isolated USB to UART <br> ~180+ user IOs |

|- | |- | ||

|} | |} | ||

| Line 13: | Line 13: | ||

The HiRADDA set is composed of two or more boards : | The HiRADDA set is composed of two or more boards : | ||

* '''HiRADDA Core''' | * '''HiRADDA Core''' | ||

| − | * '''HiRADDA Power''' | + | * '''[[Hardware/FPGARackHiRADDAPOWERV1|HiRADDA Power]]''' |

* ''n'' x user extension boards | * ''n'' x user extension boards | ||

| − | HiRADDA is compatible with the [[Hardware/FPGARackBackplane|FPGA Rack Backplane]] for interconnecting different boards with the help of the HVME16/32 version of the [[Standards/ | + | HiRADDA is compatible with the [[Hardware/FPGARackBackplane|FPGA Rack Backplane]] for interconnecting different boards with the help of the HVME16/32 version of the [[Standards/HEI_'VME'_Backplane_Bus|HES-SO Backplane Bus]] and the [[Components/IP/VME|HES-SO VME IP Core]]. Additional specific hardware can be connected to HiRADDA as stackable mezzanine card. |

HiRADDA embeds multiples memories for different usecases : ''DDR3 SDRAM'' for high speed sampling/processing, ''FLASH'' for non-volatile data (including softcores code) and ''Ferroelectric/Magnetoresistive RAM'' for non-volatile user parameters/logs. | HiRADDA embeds multiples memories for different usecases : ''DDR3 SDRAM'' for high speed sampling/processing, ''FLASH'' for non-volatile data (including softcores code) and ''Ferroelectric/Magnetoresistive RAM'' for non-volatile user parameters/logs. | ||

| − | [[File:HIRADDA_INDEV_3DVIEW.png| | + | = Showroom = |

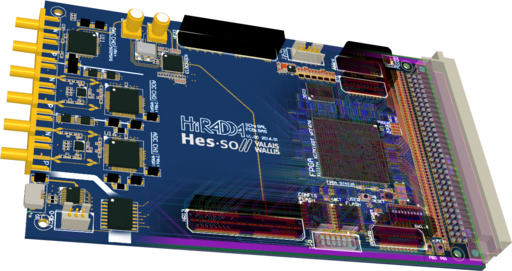

| + | [[File:HIRADDA_INDEV_3DVIEW.png|512px|HiRADDA Core V1.00 PCB 3D View]] | ||

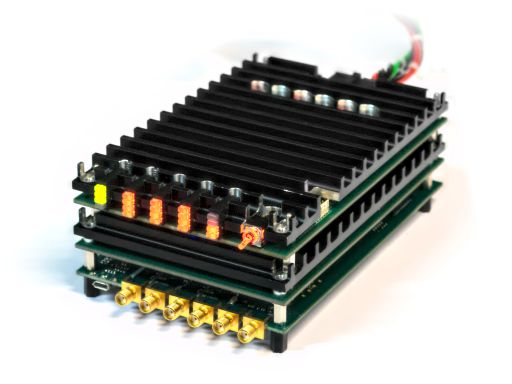

| + | [[File:HIRADDA_POWER_WITHCORE.jpg|512px|Partial HiRADDA Core & Power boards stack (Core without heatsink)]] | ||

| + | [[File:hiradda-thermal.png|512px|Thermal view of partial HiRADDA Core (no heatsink) & Power boards stack ('idle' mode)]] | ||

= Core features = | = Core features = | ||

| Line 77: | Line 80: | ||

= VME connector considerations = | = VME connector considerations = | ||

* No power rail are connected to the VME connector. | * No power rail are connected to the VME connector. | ||

| − | * The I/O bank which interfaces the VME connector can be 1.8V, 2.5V or 3.3V depending on the jumper | + | * The I/O bank which interfaces the VME connector can be 1.8V, 2.5V or 3.3V depending on the 'V@xVME' jumper position. Be careful with other FPGA Rack boards using a different voltage configuration (usually 3.3V). |

= Programming = | = Programming = | ||

| Line 90: | Line 93: | ||

= Changelog / Known issues = | = Changelog / Known issues = | ||

| − | '''Validated functions on PCB version 1. | + | '''Validated functions on PCB version 1.0.0 :''' |

* '''[PASS]''' FPGA and JTAG | * '''[PASS]''' FPGA and JTAG | ||

* '''[PASS]''' FPGA boot via SPIx4 FLASH | * '''[PASS]''' FPGA boot via SPIx4 FLASH | ||

| Line 96: | Line 99: | ||

* '''[PASS]''' AD9517-4 clock generator/distributor (include heavy configuration though SPI). | * '''[PASS]''' AD9517-4 clock generator/distributor (include heavy configuration though SPI). | ||

* '''[PASS]''' MAX5555 DAC | * '''[PASS]''' MAX5555 DAC | ||

| − | * '''[PASS]''' ADS1675 ADC CH0 and CH1 via AOP (bipolar powering). | + | * '''[PASS]''' ADS1675 ADC CH0 and CH1 via AOP (uni+bipolar powering). |

| − | * '''[ | + | * '''[PASS]''' User FRAM ''(see issues)'' : Tested with patch. |

* '''[PENDING]''' DDR3 ''(see issues)'' : Currently one step in calibration startup procedure fails. | * '''[PENDING]''' DDR3 ''(see issues)'' : Currently one step in calibration startup procedure fails. | ||

| − | * '''[TODO]''' User FLASH. ( | + | * '''[TODO]''' User FLASH. (Very low risk, low priority, when RISCV softcores are implemented) |

| − | * '''[ | + | * '''[PASS/PENDING]''' User I/Os. (HVME & extension bank HP33 not tested yet (no real risk on them). Others sucessfully.) |

* '''[TODO]''' User GTXs. (Very low priority, for future PCI-Express 8x link) | * '''[TODO]''' User GTXs. (Very low priority, for future PCI-Express 8x link) | ||

| Line 114: | Line 117: | ||

** MAX1510ETB's REFIN is accidentally bridged to +D1.5VF. | ** MAX1510ETB's REFIN is accidentally bridged to +D1.5VF. | ||

** C127 is useless (must be connected to +D1.5VF). | ** C127 is useless (must be connected to +D1.5VF). | ||

| − | * '''[Non critical]''' FPGA Bank 34. T7 (MISCIO_SWITCH8) VRP pin must be pulled up with 100Ohms and U4 (MISCIO_SWITCH0) | + | * '''[Non critical]''' FPGA Bank 34. T7 (MISCIO_SWITCH8) VRP pin must be pulled up with 100Ohms and U4 (MISCIO_SWITCH0) VRN pins pulled down with the same value. This is for DCI inputs (data lane). Therefore these SWITCH I/Os are no more usable (maybe cut concerned pins for avoid "on-demand" DDR3 crash ^^). |

* '''[Information]''' DDR3: Below 400MHz operations, FPGA internal reference is activable. At higher frequency, you will be frustrated with W4 (MISCIO_BUTTON0), AD3 (DDR3-TDQS_N) and even more with Xilinx MIG7 coregen util... | * '''[Information]''' DDR3: Below 400MHz operations, FPGA internal reference is activable. At higher frequency, you will be frustrated with W4 (MISCIO_BUTTON0), AD3 (DDR3-TDQS_N) and even more with Xilinx MIG7 coregen util... | ||

* '''[Information]''' Phantom signals on bank 14 (K23 DAC1_PD and J23 DAC1_SEL0). To know for another revision. | * '''[Information]''' Phantom signals on bank 14 (K23 DAC1_PD and J23 DAC1_SEL0). To know for another revision. | ||

| − | '''Planned changes for PCB version 1. | + | '''Planned changes for PCB version 1.1.0 :''' |

* F/MRAM good IC layout. | * F/MRAM good IC layout. | ||

* Pulldown terms on DAC LVPECL clock at the end of the line (and simplification of front elements). | * Pulldown terms on DAC LVPECL clock at the end of the line (and simplification of front elements). | ||

| Line 134: | Line 137: | ||

'''Project manager :''' | '''Project manager :''' | ||

* [[User:Cof|François Corthay]] | * [[User:Cof|François Corthay]] | ||

| − | '''Design/Schematics :''' | + | '''Main developper (Design/Schematics) :''' |

* [[User:Gal|Alexandre Ganchinho]] | * [[User:Gal|Alexandre Ganchinho]] | ||

'''PCB routing :''' | '''PCB routing :''' | ||

Latest revision as of 11:20, 28 March 2018

|

The main purpose behind this board is to have a powerful development FPGA board specialized in high-resolution data acquisition and processing. It can be used for general purpose developement too, thanks to the generous I/Os and power voltages count available for stackable extension boards.

| Type | FPGA Rack | Documentation | Description |

|---|---|---|---|

| V1.00 |  |

Full documentation |

Kintex7 XC7K160T-xFFG676 2x ADS1675 1x MAX5888 1x AD9517-4 DDR3, NOR Flash, F/MRAM Isolated USB to UART ~180+ user IOs |

The HiRADDA set is composed of two or more boards :

- HiRADDA Core

- HiRADDA Power

- n x user extension boards

HiRADDA is compatible with the FPGA Rack Backplane for interconnecting different boards with the help of the HVME16/32 version of the HES-SO Backplane Bus and the HES-SO VME IP Core. Additional specific hardware can be connected to HiRADDA as stackable mezzanine card.

HiRADDA embeds multiples memories for different usecases : DDR3 SDRAM for high speed sampling/processing, FLASH for non-volatile data (including softcores code) and Ferroelectric/Magnetoresistive RAM for non-volatile user parameters/logs.

Showroom

Core features

Main board

This 160x100mm (Eurocard) 16 layers PCB contains the following parts :

- 2x A/D 24bits 4MSPS (Ti ADS1675) with 2 analog paths :

- Direct (differential)

- Through operational amplifier (single/differential)

- 1x D/A 16bits 500MSPS (Maxim MAX5888), current source, with 1 analog path :

- Direct (differential)

- 1x Xilinx Kintex7 XC7K160T-xFFG676 (XC7K70T/XC7K325T compatible)

- 162.24k logic cells, 25.35k slices (max 2.188Mb of distributed RAM)

- 11.7Mb block RAM (650x18Kb / 325x36Kb)

- 600 DSP Slices

- GTX I/Os

- 1x Low-jitter clock generator/distributor for ADC/DAC/DDR3/FPGA (AD9517-4 with 1.6GHz VCO)

- 1x 100MHz quartz for boot clock

- 1x expansion connectors with the following FPGA banks :

- Full HR bank 13 (with 24 diffs or 48 single-ended + 2 single-ended, total 50 pins / Voltage range : 1.14V to 3.465V).

- Full HP bank 33 (with 24 diffs or 48 single-ended + 2 single-ended, total 50 pins / Voltage range : 1.14V to 1.89V).

- Full GTX banks 115 & 116 (8x TX ,8x RX, 4x reference clocks) - for PCI-Express 8x, SATA, SFP etc... use.

- 1x additional connector with 8 I/Os (+3.3V).

- 1x fully isolated USB2.0<->UART interface with hardware flow control.

- 1x additional connector with isolated 2x input and 2x output (reduce some UART functionnalities if used).

- Various memories for work/parameters :

- 1x 256MiB DDR3 (32M x 8banks x 8bit width)

- 2x 32MiB Serial QuadSPI NOR Flash (one reserved for FPGA programming, bigger compatible ones available)

- 1x 256KiB Serial SPI Ferroelectric-RAM (pin compatible Magnetoresistive-RAM can be soldered too, bigger compatible ones available)

- 4x user RGB LEDs

- 10x user DIL switches

- 1x JTAG connector

- 1x DIN41612 VME compatible connector 3x32 pins (full HVME32, 1.8V/2.5V/3.3V) with CMOS AC termination on all signal pins (default: unsoldered)

Power supply considerations

The following power rails have to be produced on the HiRADDA Power board :

- +C2.5V (AD9517-4)

- +C3.3V (AD9517-4)

- -A5.0V - Optional, for AOP input range extension

- +A1.0V - Optional, for FPGA GTX I/Os.

- +A1.2V - Optional, for FPGA GTX I/Os.

- +A1.8V - Optional, for FPGA GTX I/Os.

- +A3.3V (MAX5888)

- +A5.0V (ADS1675)

- +D1.0V (FPGA Core)

- +D1.5V (DDR3 SDRAM Core)

- +D1.8V - Optional, for user I/Os

- +D2.5V (LVDS VCXO, user I/Os)

- +D3.0V (ADS1675)

- +D3.3V (multiple usage, incl. user I/Os)

The following power rails are produced locally on the core board :

- +DR0.75V (DDR3 SDRAM Core)

- +AR2.5V (ADC)

- +AR3.0V (ADC)

VME connector considerations

- No power rail are connected to the VME connector.

- The I/O bank which interfaces the VME connector can be 1.8V, 2.5V or 3.3V depending on the 'V@xVME' jumper position. Be careful with other FPGA Rack boards using a different voltage configuration (usually 3.3V).

Programming

The FPGA on this board can be programmed in 2 ways :

- directly through JTAG interface.

- automatically on boot via the onboard FLASH memory. This serial FLASH can be accessed in :

- SPI SDR x1 : ~20s boot time

- SPI SDR x4 : ~ 5s boot time

- SPI DDR xn is not supported.

More explanation about FLASH programming is available here.

Changelog / Known issues

Validated functions on PCB version 1.0.0 :

- [PASS] FPGA and JTAG

- [PASS] FPGA boot via SPIx4 FLASH

- [PASS] FPGA boot oscillator.

- [PASS] AD9517-4 clock generator/distributor (include heavy configuration though SPI).

- [PASS] MAX5555 DAC

- [PASS] ADS1675 ADC CH0 and CH1 via AOP (uni+bipolar powering).

- [PASS] User FRAM (see issues) : Tested with patch.

- [PENDING] DDR3 (see issues) : Currently one step in calibration startup procedure fails.

- [TODO] User FLASH. (Very low risk, low priority, when RISCV softcores are implemented)

- [PASS/PENDING] User I/Os. (HVME & extension bank HP33 not tested yet (no real risk on them). Others sucessfully.)

- [TODO] User GTXs. (Very low priority, for future PCI-Express 8x link)

Issues for PCB version 1.00 :

- [Non critical] FPGA VCCBRAM is routed to +A1.0V instead of +D1.0V. Must be bridged to +D1.0V through the filter LC21.

- [Non critical] Error in PCB layout for the F/M-RAM IC : can't be soldered. Please add one (or two) SPI version through I/O port J6. See patch A.

- [Enhancement] Light overshoot on ADC 32MHz CMOS input clocks. Better to add a termination.

- [Information] LVPECL DAC clock must be only pulldowned, then decoupled (no bridge/diff term at end).

- [Critical] Errors around DDR3 power supplies (One wire was accidentally moved on schematics...). [Corrections on patch A]

- +D1.5VF is not connected to +D1.5V (filter missing!). DDR3 is NOT powered - fortunately.

- MAX1510ETB's VCC is connected to +D1.5VF instead of +D3.3V. Can't work.

- MAX1510ETB's PGOOD (open-drain) pullup resistor is missing (so the tiny testpoint is useless).

- MAX1510ETB's REFIN is accidentally bridged to +D1.5VF.

- C127 is useless (must be connected to +D1.5VF).

- [Non critical] FPGA Bank 34. T7 (MISCIO_SWITCH8) VRP pin must be pulled up with 100Ohms and U4 (MISCIO_SWITCH0) VRN pins pulled down with the same value. This is for DCI inputs (data lane). Therefore these SWITCH I/Os are no more usable (maybe cut concerned pins for avoid "on-demand" DDR3 crash ^^).

- [Information] DDR3: Below 400MHz operations, FPGA internal reference is activable. At higher frequency, you will be frustrated with W4 (MISCIO_BUTTON0), AD3 (DDR3-TDQS_N) and even more with Xilinx MIG7 coregen util...

- [Information] Phantom signals on bank 14 (K23 DAC1_PD and J23 DAC1_SEL0). To know for another revision.

Planned changes for PCB version 1.1.0 :

- F/MRAM good IC layout.

- Pulldown terms on DAC LVPECL clock at the end of the line (and simplification of front elements).

- DDR3 regulator full review (patch A integration).

- VRP/VRN resistors on DDR3 dedicated bank.

- Add external VREF on DDR3 dedicated bank for a 2x datarate enhancement (bonus).

- FPGA VCCBRAM to +D1.0V.

- CMOS AC terminations on ADC clocks.

- That's a powerful board... but less bright blue / RGB LEDs (max 0.5...1mA!) will be fine for eyes ;-)

- Add reset manager for HiRADDA Core usage without HiRADDA Power board ?

Contacts / Collaborators

This board was initially targeted for Dominique Roggo's and Joseph Moerschell's projects.

Project manager :

Main developper (Design/Schematics) :

PCB routing :

- Steve Gallay (HiRADDA Core)

- Acurdi Carmine (HiRADDA Power)

Additionnal checks :

- Blaise Evequoz (HiRADDA Core : ADC/DAC zone check)

- Gregory Emery (HiRADDA Core : General check + HiRADDA Power)

- Joseph Moerschell (HiRADDA Core : ADC/DAC/Power zone check + HiRADDA Power)

- Louis Mayencourt (HiRADDA Core : Fast general check)

VHDL/SpinalHDL dev & physical tests :